C 2005 by Ruchira Sasanka. All rights reserved.

# ENERGY EFFICIENT SUPPORT FOR ALL LEVELS OF PARALLELISM FOR COMPLEX MEDIA APPLICATIONS

BY

### RUCHIRA SASANKA

B.S., University of Moratuwa, 1998 M.S., University of Illinois at Urbana-Champaign, 2002

### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2005

Urbana, Illinois

### Abstract

Real-time complex media applications are becoming increasingly common on general-purpose systems such as desktop, laptop, and handheld computers. However, real-time execution of such complex media applications needs a considerable amount of processing power that often surpasses the capabilities of current superscalar processors. Further, high performance processors are often constrained by power and energy consumption, especially in the mobile systems where media applications have become popular.

The objective of this dissertation is to develop general-purpose processors that can meet the performance demands of future media applications in an energy-efficient way, while also continuing to work well on other common workloads for desktop, laptop, and handheld systems.

Fortunately, most media applications have a lot of *parallelism* that can be exploited for energyefficient high-performance designs. Media applications exhibit multiple types of parallelism: threadlevel parallelism (TLP), data-level parallelism (DLP), and instruction-level parallelism (ILP). In this work, we investigate exploiting all these three forms of parallelism to provide both high performance and energy efficiency.

This dissertation makes three broad contributions. First, we analyze the parallelism in complex media applications and make the case that contemporary media applications require efficient support for multiple types of parallelism, including ILP, TLP, and various forms of data-level parallelism such as sub-word SIMD, short vectors, and streams.

Second, to find the most energy efficient way of exploiting TLP, we perform a comparison between chip multi-processing (CMP) and simultaneous multi-threading (SMT). We perform this comparison for a large number of performance points derived using different processor architectures and frequencies/voltages. From this study, we find that, at equal performance, CMP is more energy efficient than SMT, especially when supporting four or more threads. We also find that the best SMT and the best CMP configuration for a given performance target have different architecture and frequency/voltage. From our analysis, we find that the relative energy efficiency depends on a subtle interplay between various factors such as capacitance, voltage, IPC, frequency, and the level of clock gating, as well as workload features. Although CMP shows a clear energy advantage for four-thread (and higher) workloads, it comes at the cost of increased silicon area. We therefore investigate a hybrid solution where a CMP is built out of SMT cores, and find it to be an effective compromise. We use this hybrid architecture as the basis for providing ILP and TLP for our new architecture described next.

Finally, based on the results of the above two studies, we propose a complete architecture, called ALP, that effectively supports all levels of parallelism described above in an energy efficient way, using an evolutionary programming model and hardware. The most novel part of ALP is a DLP technique called SIMD vectors and streams, which is integrated within a conventional superscalar based CMP/SMT architecture with sub-word SIMD. This technique lies between sub-word SIMD and vectors, providing significant benefits over the former at a lower cost than the latter. Our evaluations show that each form of parallelism supported by ALP is important. Specifically, SIMD vectors and SIMD streams are effective – compared to a system with the other enhancements in ALP, they give speedups of 1.1X to 3.4X and energy-delay product improvements of 1.1X to 5.1X for applications with DLP.

More broadly, our results show that conventional architectures augmented with evolutionary mechanisms can provide high performance and energy savings for complex media applications without resorting to radically different architectures and programming paradigms.

## Acknowledgements

I would like to express my heartfelt gratitude to Prof. Sarita Adve, who served as my thesis advisor for five years. Her insights and attention to detail were instrumental in achieving my academic goals. I would also like to thank members of my Ph.D. committee, Prof. Marc Snir, Prof. Josep Torrellas, Prof. Sanjay Patel, and Prof. Craig Zilles for the valuable feedback I received, especially at my preliminary exam.

I would also like to thank my mentors from Intel, Yen-Kuang Chen (YK) and Eric Debes who provided valuable insights into the applications we were studying. They provided the essential industrial perspective for all my research work.

I was fortunate to work with Chris Hughes, who guided my early days of research. He was both a friend and a mentor and his advice was invaluable in avoiding many pitfalls encountered in the first years as a graduate student.

I would like to thank the members of the RSIM group: Alex, Jayanth, Jerry, Rohit, and Vibhore. Alex was especially helpful with the ALP project and did a wonderful job as the application wizard.

I also extend my gratitude to Intel corporation for providing me with an Intel graduate fellowship in my fifth year of graduate studies. I would also like to acknowledge the following funding for this work: a gift from Intel corporation, an equipment donation from AMD Corp., and grants from the National Science Foundation (Grant No. CCR-0209198 and EIA-0224453).

Last but not least, I thank my parents, wife, and son, who helped me endure the hardships of being a graduate student.

# **Table of Contents**

| Chapter | 1 Introduction                                                        | 1  |

|---------|-----------------------------------------------------------------------|----|

| 1.1     | Motivation and Objective                                              | 1  |

|         | 1.1.1 Exploiting Parallelism for Performance and Energy Efficiency    | 2  |

| 1.2     | Contributions                                                         | 3  |

|         | 1.2.1 Analysis of Parallelism                                         | 4  |

|         | 1.2.2 Comparison of Alternatives for Energy-Efficient Support for TLP | 5  |

|         | 1.2.3 ALP                                                             | 6  |

| 1.3     | Thesis Organization                                                   | 8  |

| Chapter | 2 Complex Media Applications and Parallelism                          | 9  |

| 2.1     | Overview of Results                                                   | 9  |

| 2.2     | Media Applications                                                    | 12 |

|         | 2.2.1 MPEG 2 Encoder (MPGenc)                                         | 12 |

|         | 2.2.2 MPEG-2 Decoder (MPGdec)                                         | 15 |

|         | 2.2.3 Ray Tracing (RayTrace)                                          | 16 |

|         | 2.2.4 Speech Recognition (SpeechRec)                                  | 17 |

|         |                                                                       | 20 |

| 2.3     |                                                                       | 21 |

| 2.4     | Results                                                               | 24 |

|         | 2.4.1 TLP                                                             | 24 |

|         | 2.4.2 DLP                                                             | 25 |

|         |                                                                       | 30 |

|         |                                                                       | 31 |

|         |                                                                       | 35 |

|         |                                                                       | 38 |

| 2.5     | Summary                                                               | 39 |

| Chapter | 3 The ALP Programming Model                                           | 40 |

| 3.1     | SIMD Vectors (SVectors)                                               | 40 |

| 3.2     | SIMD Stream (SStreams)                                                | 43 |

| 3.3     | SVectors/SStreams vs. SIMD                                            | 44 |

|         | 3.3.1 Performance Benefits                                            | 44 |

|         | 3.3.2 Energy Benefits                                                 | 46 |

| 3.4     |                                                                       | 47 |

| Chapter | : 4 Implementation of ALP $\ldots \ldots 48$               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1     | Support for ILP, TLP, and SIMD                                                                                                                        |

| 4.2     | Support for SIMD Vectors                                                                                                                              |

|         | 4.2.1 Modifications to the Caches                                                                                                                     |

|         | 4.2.2 Modifications to the Rest of the Core                                                                                                           |

| 4.3     | Support for SIMD Streams                                                                                                                              |

| 4.4     | Support for SIMD Screams                                                                                                                              |

| 1.1     | Summary                                                                                                                                               |

| Chapter | 5 Evaluation of ALP                                                                                                                                   |

| 5.1     | Experimental Methodology                                                                                                                              |

| 5.2     | Results                                                                                                                                               |

|         | 5.2.1 Overall Results                                                                                                                                 |

|         | 5.2.2 Analysis of SIMD Vectors/Streams                                                                                                                |

|         | 5.2.3 Sensitivity to Memory and SVR Latency                                                                                                           |

| 5.3     | Discussion                                                                                                                                            |

| 0.0     | 5.3.1 SVector/SStream Design Tradeoffs and Enhancements                                                                                               |

| 5.4     | Summary                                                                                                                                               |

| 0.4     | Summary                                                                                                                                               |

| Chapter | 6 Energy Efficient TLP Support                                                                                                                        |

| 6.1     | Introduction                                                                                                                                          |

| 0.1     | 6.1.1 Sources of Complexity and Our Solutions                                                                                                         |

|         | 6.1.2 Findings                                                                                                                                        |

|         | 6.1.2       Findings       73         6.1.3       Broader Implications       74                                                                       |

| 6.9     | *                                                                                                                                                     |

| 6.2     | Experimental Methodology                                                                                                                              |

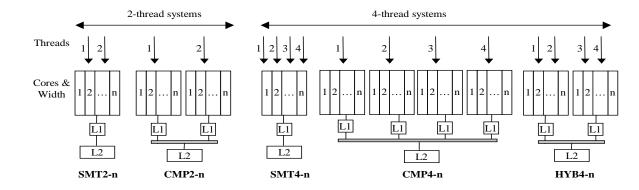

|         | 6.2.1 Systems Modeled                                                                                                                                 |

|         | 6.2.2 Workloads                                                                                                                                       |

|         | 6.2.3 Simulation Environment and Methodology                                                                                                          |

|         | 6.2.4 Metrics and Representation of Collected Data                                                                                                    |

| 6.3     | Results                                                                                                                                               |

|         | 6.3.1 Results Across All Configurations                                                                                                               |

|         | 6.3.2 The Best Core Architectures                                                                                                                     |

|         | 6.3.3 Analysis of the Results                                                                                                                         |

|         | 6.3.4 Implications of Results                                                                                                                         |

|         | 6.3.5 Energy-Delay Product (EDP) and Other Metrics                                                                                                    |

| 6.4     | Summary                                                                                                                                               |

|         |                                                                                                                                                       |

| Chapter | 7 Related Work $\ldots \ldots \ldots$ |

| 7.1     | Application Analysis                                                                                                                                  |

| 7.2     | ALP                                                                                                                                                   |

| 7.3     | Comparison of CMP and SMT                                                                                                                             |

|         |                                                                                                                                                       |

| Chapter | 8 Conclusions and Future Work                                                                                                                         |

| 8.1     | Conclusions                                                                                                                                           |

| 8.2     | Future Work                                                                                                                                           |

|         | 8.2.1 Effect of Real-time Scheduling                                                                                                                  |

|         | 8.2.2 Adaptations                                                                                                                                     |

|         | 8.2.3 Comparison of SVectors/SStreams with Conventional Vectors                                                                                       |

|         | 8.2.4 Applications and Workloads                                                                                                                      |

| 8.2.5          | Design  | of Mei | mory | Syst | em . | <br> | <br> | <br>• | <br> | <br>• | <br> | • | <br>• | • • | 113 |

|----------------|---------|--------|------|------|------|------|------|-------|------|-------|------|---|-------|-----|-----|

| References     |         |        |      |      | •••  | <br> | <br> |       | <br> |       | <br> |   | <br>• |     | 114 |

| Author's Biogr | raphy . |        |      |      |      | <br> | <br> |       | <br> |       | <br> |   |       |     | 120 |

# Chapter 1 Introduction

### **1.1** Motivation and Objective

Real-time media applications are becoming increasingly common on general-purpose systems such as desktops, laptops, tablet PCs, and handheld computers [17]. Users of such devices are using media applications for communication (e.g., video conferencing), entertainment (e.g., watching/creating movies, virtual reality, Internet, gaming), authentication (e.g., face recognition), and as a part of the human computer interface (e.g., speech/handwriting recognition). Although system designers have resorted to application specific processors (ASICs) to cater to media applications, general-purpose processors are becoming popular for these applications. This is mainly because of the growing realization that programmability is important for this application domain as well, due to a wide range of complex multimedia applications, multiple standards, and proprietary solutions. However, real-time execution of media applications on general-purpose processors faces two principal challenges:

- Performance: Real-time execution of complex media applications needs a considerable amount of processing power that often surpasses the capabilities of current superscalars. Due to their real-time nature, temporal correctness (i.e., meeting a given deadline) is as important as functional correctness (i.e., producing the correct output).

- Energy Efficiency: High performance processors are often constrained by power/energy consumption, especially in the mobile systems where media applications have become popular.

The objective of this dissertation is to develop general-purpose processors that can meet the performance demands of future media applications in an energy-efficient way, while also continuing to work well on other common workloads for desktop, laptop, and handheld systems.

To meet the above challenges and fulfill our objective, we resort to one key opportunity presented by these applications, viz., *parallelism*. Most media applications have a lot of parallelism in the form of Data Level Parallelism (DLP), Thread Level Parallelism (TLP), and Instruction Level Parallelism (ILP) that can be exploited for energy-efficient high-performance designs. This work investigates the nature of parallelism in complex media applications and how to exploit that parallelism in general-purpose architectures for better performance and energy efficiency.

### 1.1.1 Exploiting Parallelism for Performance and Energy Efficiency

All three forms of parallelism can be used for achieving both high performance and high energy efficiency. For instance, supporting DLP, TLP, and/or ILP allows more operations to be carried out in a cycle and hence increases performance. Similarly, encoding multiple operations with one instruction with DLP allows more energy efficient use of instructions. Further, the performance gain resulting from all three forms of parallelism can be used to increase the energy efficiency by employing lower frequencies/voltages and by reducing the duration of static (leakage) power consumption. However, current general purpose superscalar processors are mostly effective in exploiting ILP and, further, there is a large body of work concerning improving ILP on such processors. Consequently, this dissertation investigates and proposes ways of exploiting DLP and TLP in media applications for both high performance and energy efficiency.

#### State-of-the Art

There are several classes of machines that target media applications. Commercial general-purpose processors support sub-word SIMD instructions *(SIMD for short)* like Intel MMX/SSE, IBM AltiVec, and Sun VIS. These instructions are well suited to handling small grain DLP (i.e., short vectors) that require frequent data shuffling and reductions. However, such support is inadequate for large amounts of DLP such as long streams and long vectors.

The conventional wisdom has been that the parallelism in media applications (especially media

kernels) is in the form of large amounts of data-level parallelism (DLP). As a result, much of the recent effort for media applications has been on architectures that target large amounts of DLP in various ways. There are several architectures that target large grain DLP in streams and long vectors; e.g., VIRAM's [43] and CODE's [44] vector architecture, Imagine's streaming architecture [1]. Such architectures exploit the regularity of large grain DLP to perform computation more efficiently but do not target TLP. SCALE's vector-threading architecture [45], attempts to cater to irregular computation by combining threads with vectors. Most quantitative evaluations of these architectures, however, are largely based on small kernels, which are easily computed in real-time on today's general-purpose processors (e.g., speech codecs such as adpcm, color conversion such as rgb2cmyk, filters such as fir, and autocorrelation). Our analysis of *complete* applications (as opposed to kernels) shows that such complex applications exhibit many forms of parallelism including many granularities of DLP.

Chapter 7 further discusses the primary differences of our work from existing solutions for parallelism and media applications.

### **1.2** Contributions

This dissertation makes three high level contributions:

- 1. Analysis of parallelism in complex media applications. We characterize the parallelism and performance in complex media applications and make the case that such applications exhibit multiple types of parallelism including ILP, TLP, and multiple forms of DLP such as subword SIMD, short vectors, streams, and vectors and streams of sub-word SIMD. The last form exploits two dimensional parallelism; i.e., a vector of (short) vectors.

- A comparison of alternatives for determining the most energy efficient way to exploit TLP in media workloads on general-purpose processors.

- 3. A complete architecture, called ALP, that effectively supports all levels of parallelism described above in an energy-efficient way, using an evolutionary programming model and hardware. This is the key contribution of this dissertation.

Overall, in this work, we exploit parallelism at multiple levels. We exploit ILP using standard out-of-order superscalar processors; we investigate the most energy-efficient ways to support TLP (Chapter 6) and propose new mechanisms for exploiting DLP for multimedia applications (Chapters 3 through Chapter 5).

### 1.2.1 Analysis of Parallelism

Our first contribution is a characterization of parallelism in complex media applications. In this study, we use a five complex media applications: MPEG-2 encode, MPEG-2 decode, speech recognition (Sphinx3), face recognition (CSU), and ray tracing (Tachyon). We believe such applications will be commonplace on future general-purpose systems such as desktops, laptops, and handheld computers. We also made these applications available to the public as a benchmark suite named ALPBench [50].

Chapter 5 presents a detailed analysis of these applications. The important characteristics found are listed below.

- 1. *Multiple forms of parallelism.* These applications usually exhibit multiple forms of parallelism; viz., DLP, TLP, and ILP. All these applications exhibit coarse-grain TLP. As reported by others, we also find DLP in the kernels of these applications. However, we find many large portions lack DLP and only exhibit ILP and TLP (e.g., Huffman coding in MPEG encode and ray-tracing).

- 2. Small-grain DLP. Many applications have small-grain DLP (short vectors) due to the use of packed (SIMD) data and new intelligent algorithms used to reduce computation. Packed data reduces the number of elements (words) to be processed. New intelligent algorithms introduce data-dependent control, again reducing the granularity of DLP. For example, older MPEG encoders performed a full motion search comparing each macroblock from a reference frame to all macroblocks within a surrounding region in a previous frame, exposing a large amount of DLP. Recent advanced algorithms significantly reduce the number of macroblock comparisons by predicting the "best" macroblocks to compare. This prediction is based on the results of prior searches, introducing data-dependent control between macroblock computations and reducing the granularity of DLP.

- 3. Dense representation and regular access patterns within vectors. Our applications use dense data structures such as arrays, which are traversed sequentially or with constant strides in most cases.

- 4. *Reductions.* DLP computations are often followed by reductions, which are less amenable to conventional DLP techniques (e.g., vectorization) but become significant with the reduced granularity of DLP. For example, when processing blocks (macroblocks) in MPEG using 16B packed words, reductions occur every 8 (16) words of DLP computation.

- 5. *High memory to computation ratio*. DLP loops are often short with little computation per memory access.

- Multiple forms of DLP. Our applications exhibit DLP in the form of SIMD, short vectors, long streams, and vectors/streams of SIMD. The last form can be viewed as two dimensional DLP (i.e., as an array of arrays).

The above properties heavily influenced the design of ALP, especially the novel DLP support provided in ALP.

### 1.2.2 Comparison of Alternatives for Energy-Efficient Support for TLP

Our second contribution is a comparison of TLP mechanisms to determine the most energy-efficient form of exploiting TLP on general-purpose processors. To find the most energy-efficient way of exploiting TLP, we perform a comparison between chip multi-processing (CMP) and simultaneous multithreading (SMT). Since multi-media applications require meeting a given performance target, we compare the energy efficiency of CMP and SMT at a given performance target (i.e., at equal performance). Since the performance target can change depending on the user environment parameters like the load on the system, we do this comparison for a spectrum of performance points. Further, a given performance target can be obtained by changing both the frequency and the processor architecture. Therefore, we do the above comparison for each performance point using multiple processor architectures and frequencies/voltages.

From this study, we find that, at equal performance, CMP is more energy efficient than SMT, especially when supporting four or more threads. We also find that the best SMT and the best CMP

configuration for a given performance target have different architecture and frequency/voltage. From our analysis, we find that the relative energy efficiency depends on a subtle interplay between various factors such as capacitance, voltage, IPC, frequency, and the level of clock gating, as well as workload features.

Although CMP shows a clear energy advantage for four-thread (and higher) workloads, it comes at the cost of increased silicon area. We therefore investigate a hybrid solution where a CMP is built out of SMT cores, and find it to be an effective compromise. We use this architecture as the basis for providing ILP and TLP in ALP.

### 1.2.3 ALP

Based on our findings from the above two studies, we propose ALP, an architecture that can cater to multiple forms of parallelism found in our applications. ALP differs from the state-of-the art in one or both of the following important ways. First, as described above, we focus on more complex applications. Second, due to our focus on general-purpose processors (GPPs), we impose the following constraints/assumptions on our work:

- (i) GPPs already exploit some DLP through sub-word SIMD instructions such as MMX/SSE.

- (ii) GPPs already exploit ILP and TLP respectively through superscalar cores and through chipmultiprocessing (CMP) and simultaneous multithreading (SMT).

- (iii) Radical changes in the hardware and programming model are not acceptable for well established GPPs.

Motivated by our application study and the above constraints/assumptions, we propose a complete architecture called ALP.

The properties of our applications summarized above in Section 1.2.1 motivate supporting multiple forms of parallelism including ILP, TLP, and various forms of DLP. For DLP, properties like short vector lengths, frequent reductions, and significant non-DLP parts imply that conventional solutions such as dedicated multi-lane vector units may be over-kill. For example, the Tarantula vector unit has the same area as its scalar core [19], but will likely be under-utilized for our applications. We therefore take an alternative approach in this work that aims to improve upon SIMD, but without the addition of a dedicated vector unit.

### **Overall Architecture**

To effectively support all levels of parallelism exhibited by our applications in the context of current GPP trends, ALP is based on a GPP with CMP, SMT, and SIMD. The most novel part of ALP is a technique called *SIMD vectors (SVectors)* and *SIMD streams (SStreams)* that support larger amounts of DLP than possible with SIMD. SVectors/SStreams use an evolutionary programming model and can be implemented with modest additional hardware support that is tightly integrated within a modern superscalar pipeline.

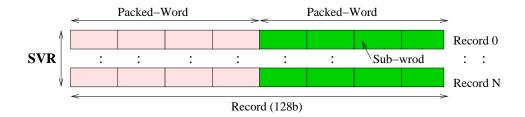

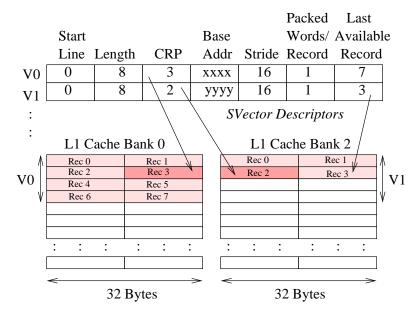

The programming model for SVectors lies between SIMD and conventional vectors. SVectors exploit the regular data access patterns that are the hallmark of DLP by providing support for conventional vector *memory* instructions. They differ from conventional vectors in that computation on vector data is performed by existing SIMD instructions. Each architectural SVector register (SVR) is associated with an internal hardware register that indicates the "current" element of the SVector. A SIMD instruction specifying an SVector register as an operand accesses and autoincrements the current element of that register. Thus, a loop containing a SIMD instruction accessing SVector register V0 marches through V0, much like a vector instruction. SStreams are similar to SVectors except that they may have unbounded length.

Our choice of supporting vector/stream *data* but not vector/stream *computation* exploits a significant part of the benefits of vectors/streams for our applications, but without need for dedicated vector/stream compute units. Specifically, ALP largely exploits existing storage and data paths in conventional superscalar systems and does not need any new special-purpose structures. ALP reconfigures part of the L1 data cache to provide a vector register file when needed (e.g., using reconfigurable cache techniques [2, 58]). Data paths between this reconfigured register file and SIMD units already exist, since they are needed to forward data from cache loads into the computation units. These attributes are important given our target is GPPs that have traditionally resisted application-specific special-purpose support.

### **Summary of Findings**

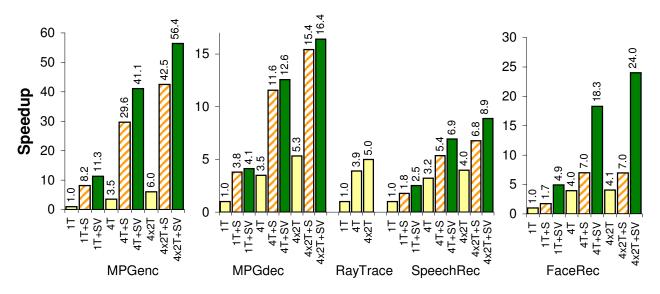

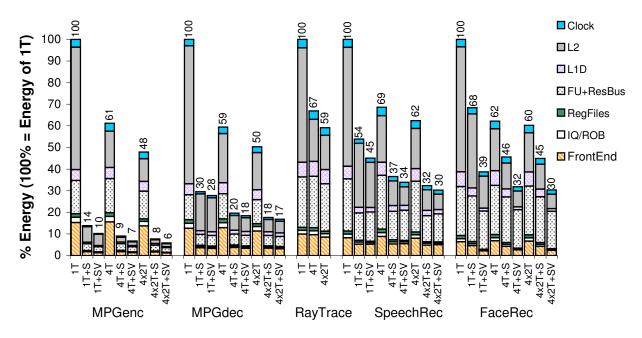

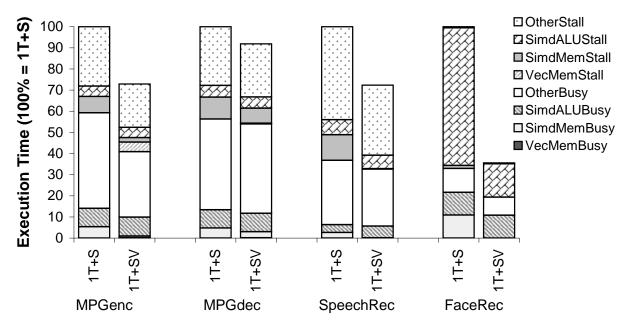

Our evaluations show that our design decisions in ALP are effective. Relative to a single-thread superscalar without SIMD, for our application suite, ALP achieves aggregate speedups from 5X to 56X, energy reduction from 1.7X to 17.2X, and energy-delay product (EDP) reduction of 8.4X to 970.4X. These results include benefits from a 4-way CMP, 2-way SMT, SIMD, and SVectors/SStreams. Our detailed results show significant benefits from each of these mechanisms. Specifically, for applications with DLP, adding SVector/SStream support to a system with all the other enhancements in ALP achieves speedups of 1.1X to 3.4X, energy savings of 1.1X to 1.5X, and an EDP improvement of 1.1X to 5.1X (harmonic mean of 1.7X). These benefits are particularly significant given that the system compared already supports ILP, SIMD, and TLP; SVectors/SStreams require a relatively small amount of hardware; and the evaluations consider complete applications.

More broadly, our results show that conventional architectures augmented with evolutionary mechanisms can provide high performance and energy savings for complex media applications without resorting to radically different architectures and programming paradigms (e.g., Imagine, SCALE).

### **1.3** Thesis Organization

ALP is motivated by the properties of complex media applications. Therefore, we first describe a characterization of several such applications in the next chapter, Chapter 2. This chapter presents a high level description of each application and a characterization of parallelism and performance of these applications.

The primary contribution of this dissertation, ALP, is described next in Chapters 3 - 5. Specifically, Chapter 3 describes the programming model and Chapter 4 describes the implementation of ALP. Chapter 5 presents an evaluation of ALP.

Chapter 6 describes the study of energy-efficient support for TLP which influenced ALP; we discuss this work after presenting ALP since the details of this work are not necessary to appreciate ALP. Finally, Chapter 7 describes the related work and Chapter 8 concludes and provides future research directions.

### Chapter 2

# Complex Media Applications and Parallelism

This chapter studies five complex media applications used in this dissertation and characterizes the nature of parallelism found in these applications. Section 2.1 provides an overview of our key results - it describes the overall properties of our media applications and our specific observations about the nature of parallelism in these complex applications. Section 2.2 describes the five complex media applications we study. Section 2.3 describes our methodology for characterizing and quantifying various forms of parallelism and finally Section 2.4 characterizes the parallelism and performance of these applications.

### 2.1 Overview of Results

In this study, we use five complex media applications: MPEG-2 encode, MPEG-2 decode, speech recognition (Sphinx3), face recognition (CSU), and ray tracing (Tachyon). We believe such applications will be commonplace on future general-purpose systems such as desktops, laptops, and handheld computers.

Since complex media applications differ considerably from small media kernels and other desktop applications in many important respects, they need to be studied on their own. Specifically, most media applications have a lot of parallelism that can be exploited for energy-efficient highperformance designs. Table 2.1 describes the three main types of parallelism that are available in media (and other) applications.

Our attempts at characterizing and exploiting various forms of parallelism in these applications

| Instruction<br>Level<br>Parallelism<br>(ILP): | If the operations in a given set are both data and control independent of one another, such a set<br>exhibits ILP. This is because each operation can be encoded as an individual instruction and can<br>be executed independent of one another. ILP can be expressed in the programming model as<br>with VLIW (Very Long Instruction Word) or EPIC (Explicitly Parallel Instruction Computing)<br>instruction sets; alternatively ILP can be dynamically discovered by out-of-order superscalar<br>processors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Level<br>Parallelism<br>(DLP):           | If the operations in a given set are (i) both data and control independent of one another and (ii) have the same op-code, then that set of operations exhibits DLP. Practical systems add one additional restriction to the above two; viz., data regularity. Data regularity requires that the locations (addresses/register numbers) of data items used by all operations in the set can be expressed using a simple formula so that it can be succinctly encoded in an instruction (for instance, data items can be sequential, or can have a constant stride between two consecutive items). Although it is possible to rearrange data to meet the data-regularity requirement (e.g., using scatter/gather operations in a vector architecture), such rearrangements usually have high costs. Some systems relax the requirement of control independence of operations by resorting to masking. However, masking reduces the effectiveness of DLP since masking causes unnecessary data to be loaded/processed. Further, some practical systems require a large number of operations within each set to be effective. Therefore, to obtain significant benefits using DLP, the number of operations should be relatively large, masking should be minimized, and the number of adta rearrangements to satisfy data-regularity should be small. Sets with a large number of operations are said to exhibit <i>coarse-grain DLP</i> (as opposed to <i>fine- or small-grain DLP</i> with only a few operations per set). DLP is the most restrictive form of parallelism. DLP can be degenerated into both TLP and ILP. Vector instruction sets [15, 3, 19] and sub-word SIMD instructions like Intel MMX/SSE [34] are examples of DLP instruction sets. |

| Thread<br>Level<br>Parallelism<br>(TLP):      | TLP extends the idea of independence among multiple operations to <i>multiple sets of operations</i> , where operations within each set can be dependent or independent. Each such set of operations is called a thread. Trivially, two independent sets each with one operation can create two parallel threads. However, to be useful in practice, each thread has to contain a large number of dynamic operations and must be mostly independent of the other threads; i.e., there should be only a few, if any, points of interaction between threads. In other words, only a few operations should have direct inter-set dependencies. The operations that are <i>directly</i> dependent on operations from any other set require synchronization (e.g., locks, barriers) to avoid race conditions. Note that there is no restriction on the individual operations in any set; i.e., the individual operations within a set can be either data/control dependent or independent of the other operations in the same set. Further, DLP and/or ILP can be exploited within each set, if operations within a set satisfy the requirements described above for DLP and/or ILP. POSIX threads (Pthreads) are one popular thread standard on general-purpose processors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Table 2.1: | Three | types | of | parallelism. |

|------------|-------|-------|----|--------------|

|------------|-------|-------|----|--------------|

revealed several important properties about them:

Multiple forms of parallelism. These applications usually exhibit multiple forms of parallelism like thread/data/instruction-level parallelism (TLP/DLP/ILP). All these applications exhibit coarse-grain TLP. As reported by others, we also find DLP in the kernels of these applications. However, we find many large portions lack DLP and only exhibit ILP and TLP (e.g., Huffman coding in MPEG encode and ray-tracing).

- 2. Small-grain DLP. Many applications have fine-grain DLP due to the use of packed (SIMD) data types and new intelligent algorithms used to reduce computation. Packed data reduces the number of elements (words) to be processed. New intelligent algorithms introduce data-dependent control, again reducing the granularity of DLP. For example, older MPEG encoders performed a full motion search comparing each macroblock from a reference frame to all macroblocks within a surrounding region in a previous frame, exposing a large amount of DLP. Recent advanced algorithms significantly reduce the number of macroblock comparisons by predicting the "best" macroblocks to compare. This prediction is based on the results of prior searches, introducing data-dependent control between macroblock computations and reducing the granularity of DLP.

- 3. Dense representation and regular access patterns within vectors. Our applications use dense data structures such as arrays, which are traversed sequentially or with constant strides in most cases.

- 4. *Reductions.* DLP computations are often followed by reductions, which are less amenable to conventional DLP techniques (e.g., vectorization) but become significant with the reduced granularity of DLP. For example, when processing blocks (macroblocks) in MPEG using 16B packed words, reductions occur every 8 (16) words of DLP computation.

- 5. *High memory to computation ratio*. DLP loops are often short with little computation per memory access.

- Multiple forms of DLP. Our applications exhibit DLP in the form of SIMD, short vectors (small-grain DLP), long streams (coarse-grain DLP), and vectors/streams of SIMD (two dimensional DLP).

The next section describes the complex media applications used in this study.

### 2.2 Media Applications

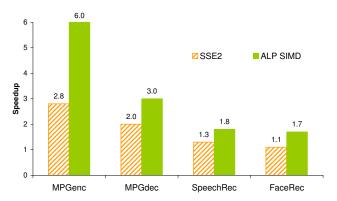

This section describes our applications and the enhancements we made to them. To extract parallelism, we threaded the applications and inserted DLP instructions in the frequently used functions. For threading, we used POSIX threads (Pthreads). For most cases, straightforward parallelization was sufficient for the relatively small systems we consider (e.g., static scheduling of threads). For SIMD, we used Intel SSE2 and and a more aggressive simulated version called ALP SIMD, which is modeled after SSE2. SIMD hand-coding is prevalent practice for these applications and the maximum number of static assembly instructions inserted for any given application is about 400 (for MPGenc). In some cases, we made a few algorithmic modifications to the original applications to improve performance.

The following descriptions provide a summary of algorithmic modifications (where applicable), major data structures, application phases, thread support, and sub-word SIMD support, and SVector/SStream support The SVector/SStream support for each application is described along with the other modifications to the corresponding application only to improve readability. The details and evaluation of SVectors are described in Chapters 3 - 5. Recall from Section 1.2.3 that SVectors/SStreams use vector/stream loads to bring in data to SVector registers (SVRs) and use ALP SIMD instructions for computation.

### 2.2.1 MPEG 2 Encoder (MPGenc)

We use the MSSG MPEG-2 encoder [56]. MPGenc converts video frames into a compressed bitstream. A video encoder is an essential component in VCD/DVD/HDTV recording, video editing, and video conferencing applications. Many recent video encoders like MPEG-4/H.264 use similar algorithms.

A video sequence consists of a sequence of input pictures. Input images are in the YUV format; i.e., one luminance (Y) and two chrominance (U,V) components. Each encoded frame is characterized as an I, P, or B frame. I frames are temporal references for P and B frames and are only spatially compressed. On the other hand, P frames are predicted based on I frames, and B frames are predicted based on neighboring I and P frames.

Modifications: We made two algorithmic modifications to the original MSSG code: (1) we use

an intelligent three-step motion search algorithm [42] instead of the original full-search algorithm and (2) we use a fast integer discrete cosine transform (DCT) butterfly algorithm based on the Chen-Wang algorithm [79] instead of the original floating point matrix-based DCT.

**Data Structures:** Each frame consists of 16x16 pixel macroblocks. Each macroblock consists of four 8x8 luminance locks and two 8x8 chrominance blocks, one for U and one for V.

**Phases:** The phases in MPEG-2 include motion estimation (ME), quantization, discrete cosine transform (DCT), variable length coding (VLC), inverse quantization, and inverse DCT (IDCT).

The first frame is always encoded as an I-frame. For an I-frame, the compression starts with DCT. DCT transforms blocks from the spatial domain to the frequency domain. Following DCT is quantization that operates on a given 8x8 block, a quantization matrix, and a quantization value. The operations are performed on each pixel of the block independent of each other. After quantization, VLC is used to compress the bit stream. VLC uses both Huffman and run-length coding. This completes the compression.

For predictive (P and B) frames, the compression starts with motion estimation. In motion estimation, for each macroblock of the frame being currently encoded, we search for a "bestmatching" macroblock within a search window in a previously encoded frame. The distance or "match" between two macroblocks is computed by calculating the sum of the differences between the pixels of the blocks. The original "full-search" algorithm performs this comparison for all macroblocks in the search window. Instead, we use a three-step search algorithm which breaks a macroblock search into three steps: (i) search at the center of the search window, (ii) search around the edges of the search window, and (iii) search around the center of the search window. A subsequent step is taken only if the previous step does not reveal a suitable match. Motion estimation is the longest (most compute intensive) phase for P and B frames. The rest of the compression for P and B frames is the same as that for an I-frame.

For processing subsequent frames, it is necessary to decode the encoded frame. For this purpose, inverse quantization and inverse DCT are applied to the encoded frame. These inverse operations have the same properties as their forward counterparts. We removed the rate control logic from this application. The original implementation performs rate control after each macroblock is encoded, which imposes a serial bottleneck. For the threaded version, rate control at the end of a frame encoding would be more efficient but we did not implement this.

**Threads:** We create a given number of threads at the start of a frame and join them at the end of that frame. Within a frame, each thread encodes an independent set of contiguous macroblock rows in parallel. Each thread takes such a set through all the listed phases and writes the encoded stream to a private buffer. Thread 0 sequentially writes the private buffers to the output.

**SIMD:** Integer SIMD instructions are added to all the phases except VLC. 1-byte (char) sub-words are used in macroblocks; 2-byte (short) words are used to maintain running sums. The main SIMD computation in motion estimation is a calculation of sum of absolute difference (SAD) between two 128b packed words of two macroblocks. PSAD (packed SAD) instructions in SSE2 are used for this purpose. The result of the SAD is accumulated in a register. For half pixel motion estimation, it is necessary to find the average of two 128b records. This is achieved using PAVG (packed average) SSE2 instructions.

We obtained optimized SSE2 code for DCT and IDCT from [30] and [31], respectively. Subword sizes of 16b (short) are used for DCT/IDCT and multiply accumulate instructions are used for common multiply accumulate combinations in this code. Quantization is a truncation operation. We use packed minimum and packed maximum for performing the truncation [34].

Before DCT and after IDCT, the encoder performs a block subtraction and a block addition where a block of frequency deltas are added or subtracted from a block. We use packed saturated addition and subtraction for these operations.

**SVectors:** SVectors are used in all the phases where SIMD is used (i.e., in all the phases except VLC). Computation uses the same SIMD compute instructions used by the SIMD implementation described above. However, recall that SVectors use vector loads instead of SIMD loads. SVectors replace SIMD loads except in parts of DCT and IDCT. DCT and IDCT each consists of two

sub parts: row DCT/IDCT and column DCT/IDCT. Because of the non-sequential memory access patterns, column DCT/IDCT uses SIMD loads instead of SVector loads. Constant coefficient tables used in row DCT, row IDCT, and quantization can be loaded into SVRs at the start of a phase and can be held throughout that phase. In motion estimation, the macroblock being encoded is loaded once and held in an SVR while it is compared against many reference blocks.

### 2.2.2 MPEG-2 Decoder (MPGdec)

We use the MSSG MPEG-2 decoder [56]. MPGdec decompresses a compressed MPEG-2 bit-stream. Video decoders are used in VCD/DVD/HDTV playback, video editing, and video conferencing. Many recent video decoders, like MPEG-4/H.264, use similar algorithms.

Data Structures: Same as for MPGenc.

**Phases:** Major phases for MPGdec include variable length decoding (VLD), inverse quantization, IDCT, and motion compensation (MC),

The decoder applies the inverse operations performed by the encoder. First, it performs variable-length Huffman decoding. Second, it inverse quantizes the resulting data. Third, the frequency-domain data is transformed with IDCT to obtain spatial-domain data. Finally, the resulting blocks are motion-compensated to produce the original pictures.

**Threads:** At first glance, this application seems to be serial since frames have to be recovered by decoding blocks one by one from the encoded bit stream. However, a closer look at the application shows that the only limitation of exploiting TLP for this application is the serial reads from the bit stream and the rest can be readily parallelized.

In our implementation, thread 0 identifies the slices (contiguous rows of blocks) in the input encoded bit-stream. When a given number of slices is identified, those slices are assigned to a new thread for decoding. Due to this staggered nature of creating threads, different threads may start (and finish) at different times, thereby reducing the thread-level scalability of the application.

Each thread takes each block in a slice through all the phases listed above and then writes

each decoded block into a non-overlapping region of the output image buffer.

**SIMD:** Integer SIMD instructions are added to IDCT and motion compensation. IDCT uses the same SIMD code used in MPGenc. Motion compensation contains sub-functions like add-block (adding the reference block and error (frequency deltas)) and saturate. These operations are performed using packed addition with saturate on 16b words.

**SVectors:** Use of SVectors in motion compensation and IDCT is similar to that for MPGenc; i.e., SVectors are used in all the phases where SIMD is used. Computation uses the same SIMD compute instructions used by the SIMD implementation described above. SVectors replace SIMD loads except in a part of IDCT. IDCT consists of two sub-parts: row IDCT and column IDCT. Because of the random memory access patterns, column IDCT uses SIMD loads instead of SVector loads. Constant coefficient tables used in row IDCT can be loaded into SVRs at the start of the IDCT phase and can be held throughout that phase.

### 2.2.3 Ray Tracing (RayTrace)

We use the Tachyon ray-tracer [72]. A ray-tracer renders a scene using a scene description. Ray tracers are used to render scenes in games, 3-D modeling/visualization, virtual reality applications, etc.

The ray tracer takes in a scene description as input and outputs the corresponding scene. A scene description normally contains the location and viewing direction of the camera, the locations, shapes, and types of different objects in the scene, and the locations of the light sources.

**Data Structures:** The constructed scene is a grid of pixels. The pixels are colored based on the light sources and objects in the scene. The objects are maintained in a linked list. The color of each pixel is determined independently.

**Phases:** This application does not have distinct phases at a high level. At start, based on the camera location and the viewing direction specified, the viewing plane is created to represent the

grid of pixels to be projected from the scene to the resulting picture. To project the correct color for each pixel, a ray is shot from the camera through the viewing plane into the scene. The ray is then checked against the list of objects to find out the first object that the ray intersects. After that, the light sources are checked to see if any of the light rays reach that intersection. If so, the color to be reflected is calculated based on the color of the object and the color of the light source. The resulting color is assigned to the pixel at where the camera ray and the viewing plane intersect. Moreover, since objects can be reflective or transparent, the ray may not stop at the first object it intersects. Instead, the ray can be reflected or refracted to other directions until another object is intersected. In that case, the color of the corresponding pixel is determined by repeatedly reflecting/refracting the ray at each surface.

**Threads:** Each thread is given N independent rays to trace, where N is the total number of pixels in the viewing plane divided by the number of threads in the system. Rays are assigned to different threads using a round-robin algorithm to achieve better load balancing.

**SIMD:** No DLP support is added since the various computations done on each ray can be quite different from neighboring rays. This is because neighboring rays can intersect different objects leading to different computations (operations) with each ray. Further, there is no DLP within each ray since each ray performs control intensive operations.

### 2.2.4 Speech Recognition (SpeechRec)

We use the CMU SPHINX3.3 speech recognizer [61]. A speech recognizer converts speech into text. Speech recognizers are used with communication, authentication, and word processing software and are expected to become a primary component of the human-computer interface in the future.

Data Structures: The major data structures used include:

(1) 39-element feature vectors extracted from an input speech sample.

(2) Multiple lexical search trees built from the language model provided. Each tree node is a3-state hidden Markov model (HMM) and describes a phoneme (sound element).

(3) Each senone (a set of acoustically similar HMM states) is modeled by a Gaussian model. Each Gaussian model contains two arrays of 39-element vectors (mean and variance) and one array of coefficients.

(4) A dictionary (hash table) of known words.

**Phases:** The application has three major phases: feature extraction, Gaussian scoring, and searching the language model/dictionary.

First, the feature extraction phase creates 39-element feature vectors from the speech sample. The Gaussian scoring phase then matches these feature vectors against the phonemes in a database. It evaluates each feature vector based on the Gaussian distribution in the acoustic model (Gaussian model) given by the user. In a regular workload, there are usually 6000+ Gaussian models. The goal of the evaluation is to find the best score among all the Gaussian models and to normalize other scores with the best one found. As this scoring is based on a probability distribution model, multiple candidates of phonemes are kept so that multiple words can be matched. The final phase is the search phase, which matches the candidate phonemes against the most probable sequence of words from the language model and the given dictionary. Similar to the scoring phase, multiple candidates of words (hypotheses) are kept so that the most probable sequence of words can be chosen.

The algorithm can be summarized as follows:

We make the root node of each lexical search tree active at start. The following steps are repeated until speech is identified. Step (i) is the feature extraction phase, (ii) is in the Gaussian scoring phase, and steps (iii) and (iv) are in the search phase.

(i) The feature extraction phase creates a feature vector from the speech sample.

(ii) A feature vector is compared against Gaussian models of most likely senones and a similarity score is computed for each senone.

(iii) For each active node in each lexical search tree, the best HMM score for it is calculated. Then the overall best HMM score among all nodes is calculated (call this  $S_{ob}$ ).

(iv) All nodes with HMM scores below  $S_{ob}$  – threshold, where threshold is a given threshold, are deactivated and the children of the still active nodes are also activated. If the node is a leaf

node with high enough score, the word is recognized and the dictionary is looked up to find the spelling.

For reporting results, the startup phase, where some data structures are initialized, is ignored since it is done only once for the entire session and it can be optimized by loading checkpointed data [55].

**Threads:** We parallelized both the Gaussian scoring and the search phase. We did not parallelize the feature extraction phase since it takes only about 2% of the execution time (with a single thread). A thread barrier is used for synchronization after each phase. To create threads for the Gaussian scoring phase, we divide the Gaussian models among threads to calculate senone scores.

In the search phase (steps (iii) and (iv) above), active nodes are divided evenly among threads. We use fine grain locking to synchronize updates to the existing hypotheses in step (iv). This locking makes this phase less scalable than the Gaussian scoring phase.

**SIMD:** We added floating point SIMD support to the Gaussian scoring phase. The SIMD computation in this phase consists of a short loop which performs multiplication and addition to calculate the score. Floating point SIMD instructions calculate the score of each feature vector and Gaussian model. Packed floating point multiplication and addition (MULPS, ADDPS) are used for this operation and 4B sub-words (floats) are used.

**SVectors:** As with SIMD, SVectors are also used with Gaussian scoring. Feature vectors are loaded only once and held in SVRs for many iterations of phase (i). Gaussian model vectors are loaded into SVRs. The same SIMD compute instructions described above are used with SVectors to calculate the Gaussian score between the feature vector and the Gaussian model vectors.

The original Sphinx code performs a pre-computation to reduce the number of Gaussian models that have to evaluated in the Gaussian scoring phase. This pre-computation reduces the total execution time of both non-SIMD and SIMD cases. Since SVectors can handle DLP more efficiently, for the SVector version, it is more beneficial to forego this pre-computation because this pre-computation is control intensive. Therefore, we do not use this pre-computation with the SVector version but evaluate all the Gaussian models in the Gaussian scoring phase.

### 2.2.5 Face Recognition (FaceRec)

We use the CSU face recognizer [7]. Face recognizers recognize images of faces by matching a given input image with images in a given database. Face recognition is used in applications designed for authentication, security, and screening. Similar algorithms can be used in other image recognition applications that perform image searches and data-mining.

This application uses a large database (called subspace) that consists of multiple images. The objective of phase recognition is to find the image in subspace that matches best with a given input image. A match is determined by taking the "distance" or difference between two images.

**Modifications:** The CSU software tries to find the pairwise distances among all images in the database since the objective of CSU software is to find the effectiveness of distance finding algorithm. We modified the application so that a separate input image is compared with each image in the subspace to emulate a typical face recognition scenario (e.g., a face of a subject is searched in a database).

**Data Structures:** Each image is a single column vector with thousands of rows. The subspace is a huge matrix where each image is a column of the matrix.

**Phases:** This application is first trained with a collection of images in order to distinguish faces of different persons. Moreover, there are multiple images that belong to the same person so that the recognizer is able to match face images against different expressions and lighting conditions. Then, the training data is written to a file so that it can be used in the recognizion phase. Since training is done offline we consider only the recognizion phase for reporting results.

At the start of the recognition phase, the training data and the image database are loaded. The image database creates the subspace matrix.

The rest of the recognition phase has two sub-phases:

(i) Projection: When an input image is given, it is normalized and projected into the large subspace matrix that contains the other images. The normalization involves subtracting the subspace's mean from the input. Then that normalized image is "projected" on to the subspace by taking the cross product between the normalized image and the subspace.

(ii) Distance computation: Computes the difference between each image in the subspace and the given image by finding the similarity (distance).

**Threads:** In the projection sub-phase, each thread is given a set of columns from the subspace to multiply. In the distance-computation sub-phase, each thread is responsible for computing distances for a subset of images in the database.

**SIMD:** Floating point double precision (8B) SIMD instructions are used for matrix computations and for distance finding. Both these sub-phases contain short loops that perform multiplication and addition/subtraction. The SIMD instructions used include packed subtraction (SUBPD), packed multiplication (MULPD), and packed addition (ADDPD).

**SVectors:** SVectors/SStreams are used within both sub-phases where SIMD instructions are used (i.e., in matrix computations and distance finding). SStreams are used for loading columns of matrices for processing in both phases. The same SIMD compute instructions described above are used with SVectors.

### 2.3 Methodology

For this study, we primarily obtain results from a CMP simulator called AlpSim. AlpSim allows us to study the parallelism and scalability of systems under different conditions. To augment these results, where practically feasible, we also present data obtained on a real Pentium 4 system.

AlpSim is an execution-driven cycle-level simulator derived from RSIM [28], and models wrong path instructions and contention at all resources. AlpSim simulates all code in C libraries but only emulates operating system calls.

With AlpSim, we model a CMP system to study the parallelism in our applications. Each CMP

| Parameter                   | Value PER                    | # of       |

|-----------------------------|------------------------------|------------|

|                             | PARTITION                    | Partitions |

| Phy Int Reg File (32b)      | 64  regs, 5 R/4 W            | 2          |

| Phy FP/SIMD Reg File (128b) | 32  regs, 4 R / 4 W          | 2          |

| Int Issue Queue             |                              | 2          |

| -# of Entries               | 24                           |            |

| -# of R/W Ports             | 3R/4W                        |            |

| -# of Tag R/W Ports         | 6R/3W                        |            |

| -Max Issue Width            | 3                            |            |

| FP/SIMD Issue Queue         |                              | 2          |

| -# of Entries               | 24                           |            |

| -# of R/W Ports             | 3R/4W                        |            |

| -# of Tag R/W Ports         | 5R/3W                        |            |

| -Max Issue Width            | 3                            |            |

| Load/Store Queue            |                              | 2          |

| -# of Entries               | 16                           |            |

| -# of R/W Ports             | 2R/2W                        |            |

| -Max Issue Width            | 2                            |            |

| Branch Predictor (gselect)  | 2KB                          | 2          |

| Integer ALUs (32b)          | 2                            | 2          |

| FP SIMD Units (128b)        | 2                            | 2          |

| Int SIMD Units (128b)       | 2                            | 2          |

| Reorder Buffer              | 32  ent, 2R/2W               | 4          |

| -Retire Width               | 2                            |            |

| Rename Width                | 4 per thread                 | 2          |

| Max. Fetch/Decode Width     | $6 (\max 4 \text{ per thr})$ | ead)       |

| Parameter            | Value PER BANK                | # Banks |

|----------------------|-------------------------------|---------|

| L1 I-Cache           | 8K, 4 Way, 32B line, 1 Port   | 2       |

| L1 D-Cache           | 8K, 2 Way, $32B$ line, 1 Port | 4       |

| (Writethrough)       |                               |         |

| L2 Cache             | 256K, 4 Way, 64B line, 1 Port | 4       |

| (Writeback, unified) |                               |         |

| Bandwidth and Contentionless Latencies @ 4 GHz |                                      |  |  |  |  |  |  |

|------------------------------------------------|--------------------------------------|--|--|--|--|--|--|

| Parameter                                      | Value (cycles @ 4 GHz)               |  |  |  |  |  |  |

| ALU/Int SIMD Latency                           | 8 (Div-32b), 2 (Mult-32b), 1 (Other) |  |  |  |  |  |  |

| FP/FP SIMD Latency                             | 12 (Div), 4 (Other)                  |  |  |  |  |  |  |

| L1 I-Cache Hit Latency                         | 2                                    |  |  |  |  |  |  |

| L1 D-Cache/SVR Hit Latency                     | 3                                    |  |  |  |  |  |  |

| L2 Cache Latency                               | 18 (hit), 256 (miss)                 |  |  |  |  |  |  |

| Memory Bandwidth                               | 16  GB/s                             |  |  |  |  |  |  |

**Table 2.2:** Base architecture parameters for AlpSim. Note that several parameter values are *per partition or bank*.

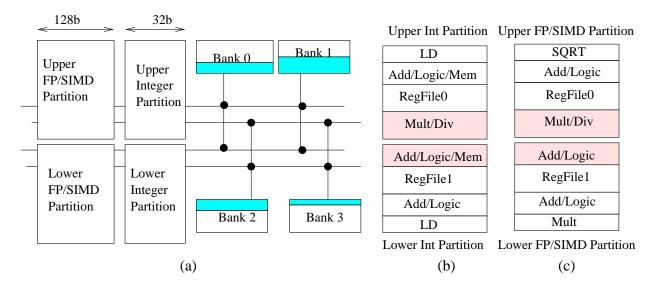

processor is an out-of-order superscalar processor and has separate private L1 data and instruction caches. All cores in the CMP share a unified L2 cache. Each thread is run on a separate CMP processor. The simulation parameters used are given in Table 2.2. Following the modern trend of general purpose processor architectures, almost all processor resources are partitioned and caches are banked.

The ALP SIMD programming model used with AlpSim roughly emulates Intel's MMX/SSE2 with multiple 8-, 16-, 32-, or 64-bit sub-words within a 128-bit word. Most common opcodes are supported; e.g., packed addition, subtraction, multiplication, absolute difference, average, horizon-tal reduction, logical, and pack/unpack operations. SIMD operations use the FP register file and FP units.

AlpSim uses SPARC binaries for non-SIMD code. Pthreads-based C code is translated into binary using the Sun cc 4.2 compiler with options -xO4 -xunroll=4 -xarch=v8plusa. DLP code resides in a separate assembly file, organized as blocks of instructions and simulated using hooks placed in the binary. When such a hook is reached while simulating, the simulator switches to the proper block of SIMD instructions in the assembly file.

To complement the results obtained using AlpSim, we obtained data using a 3.06 GHz Pentium 4 system with SSE2 running the Linux 2.4 kernel (referred to later as **P4Sys**). The processor frontside bus operates at 533 MHz (quad-pumped) and the system has 2GB of PC2100 DDR memory. The applications for P4Sys were compiled using the Intel icc compiler with maximum optimization level O3 and options -march=pentium4 -mcpu=pentium4 (for Pentium 4). We aligned data arrays at 16B boundaries for best performance as suggested in [34]. On P4Sys, we used the Intel VTune performance analyzer and used the performance counter (sampling) mode to obtain results without any binary instrumentation. Only single-thread data were obtained using the P4Sys.

The following inputs were used for each application. For MPGenc and MPGdec, DVD resolution (704x480) input streams were used. For RayTrace, a 512x512 resolution picture (a scene of a room with 20 objects) is used. For SpeechRec, a dictionary/vocabulary of 130 words was used with the input speech sample containing the words "Erase T M A Z X two thousand five hundred and fifty four". For FaceRec, a database of 173 images (resolution 130x150) was used with an input image of the same resolution.

### 2.4 Results

This section provides quantitative results about the parallelism found in our applications. Primarily, we present results using AlpSim and ALP SIMD. To augment those results, we present results obtained on a Pentium 4 processor based system for ILP and SIMD (SSE2).

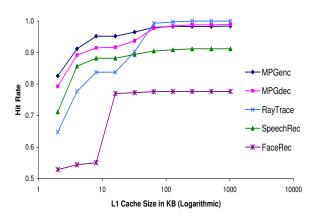

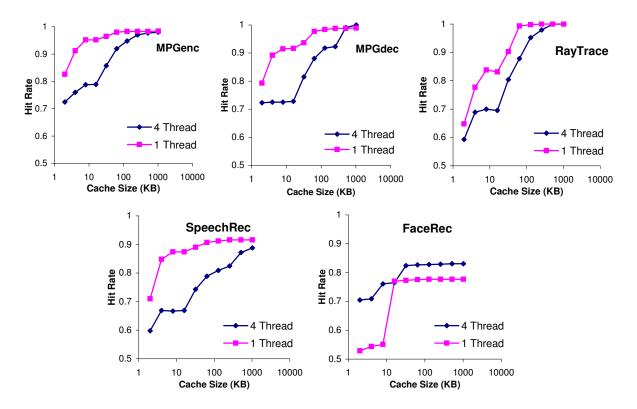

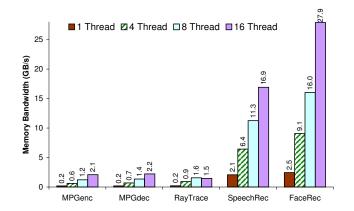

We categorize our results into several sections. First, we characterize each type of parallelism. Second, we analyze the effects of interaction between two types of parallelism (e.g., DLP and TLP). Since we observe that all types of parallelism investigated here are sensitive to the memory system parameters, in Section 2.4.5, we present data showing the size of working sets utilized by our applications, the effect of increasing memory latencies (i.e., frequency scaling), and the effect of supporting more threads on the memory bandwidth. Finally, in Section 2.4.6, we give the application-level real-time performance of our applications on the Pentium 4 system with SSE2.

Although the results we show are sensitive to the size of inputs, the overall parallelism should improve or remain the same with larger inputs for all applications.

### 2.4.1 TLP

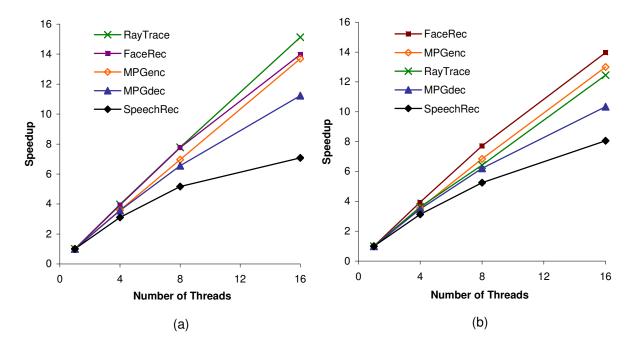

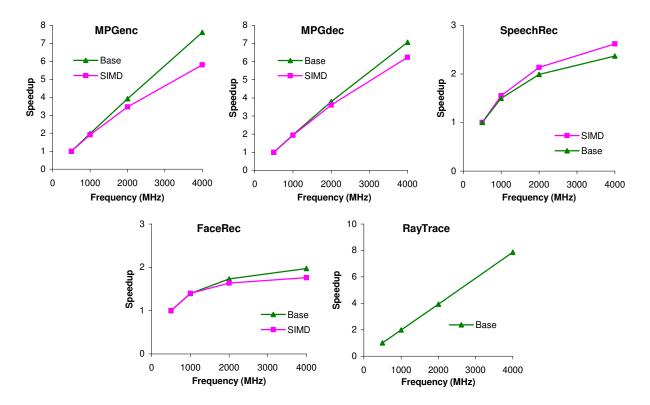

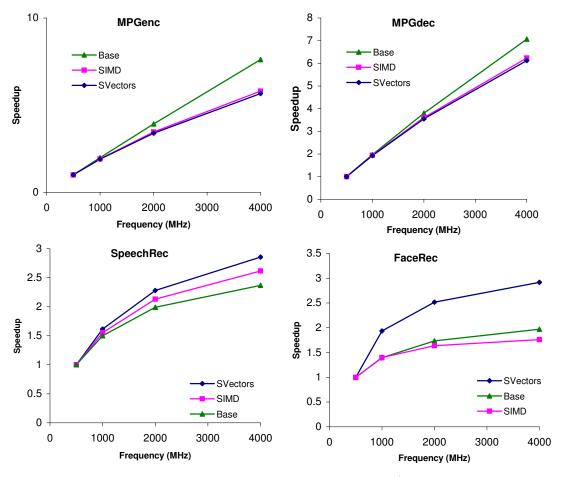

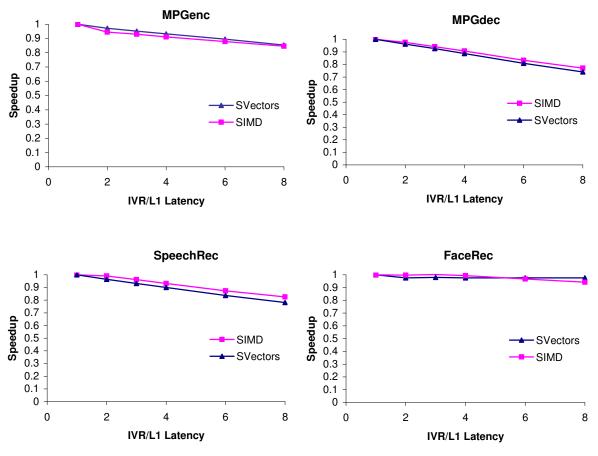

Figures 2.1(a) and (b) show the speedup achieved with multiple threads on AlpSim with a 1 cycle ideal memory system and a non-ideal memory system, respectively. The threads do not use SIMD instructions. The ideal memory system results are obtained with perfect 1 cycle L1 caches to study the TLP scalability independent of the memory system parameters, especially those of the L2 cache. These applications can be executed on systems with very different L2 configurations, from shared L2 caches to private L2 caches. Similarly, the size and the associativity of L2 caches vary widely in commercial systems. When we use high memory latencies, the scalability becomes sensitive to the particular L2 configuration as described in Section 2.4.5. Therefore, Figure 2.1(a) shows inherent TLP in applications, independent of L2 parameters. However, since it is useful to see how these applications will behave on a practical machine, Figure 2.1(b) shows TLP scalability for the system described in Section 2.3 except for one change; these results use a 16-way, 16MB L2 cache with 64 GB/s memory bandwidth to support up to 16 threads.

As shown in Figure 2.1, MPGenc, MPGdec, FaceRec, and RayTrace scale well up to 16 threads with both ideal and realistic memory parameters since the threads are independent and hence do not require extensive synchronization. For MPGenc, there are two limitations to obtaining ideal scalability characteristics: (i) serialization present at the end for writing private buffers, and (ii) imperfect load balancing due to different threads performing different amount of work. The scalability of MPGdec can be further improved by addressing the current limitations to its scalability, namely, (i) staggered thread creation, and (ii) load imbalance. With larger inputs (e.g., HDTV), the former has less effect (HDTV input improved the speedup of 16 threads by 14%-15% for both ideal and realistic memory parameters). The latter may be improved by dynamic slice assignment [26].

The thread scalability of SpeechRec is somewhat limited. Its scalability can be slightly improved by threading the feature extraction phase as well. However, the scalability of coarse-grained threads in SpeechRec is mainly limited by the fine grain synchronization (locking) used in the search phase [47]. However, we found that larger dictionaries increase the thread scalability. Note that multi-threaded versions of SpeechRec achieve slightly better speedups with realistic memory parameters. In that case, the execution time of the single thread version is dominated by the time stalled for memory. The multi-threaded version can reduce that stall time considerably due to memory parallelism offered by multiple threads. However, with ideal memory parameters, the multi-threaded version cannot reduce the memory access time any further. Therefore, synchronization has a larger negative effect on the multi-threaded versions with ideal memory parameters.

### 2.4.2 DLP

|                    | MPGenc | MPGdec | SpeechRec  | FaceRec     |

|--------------------|--------|--------|------------|-------------|

| Sub-word size      | 1B,2B  | 1B,2B  | 4B (float) | 8B (double) |

| % SIMD instr.      | 24     | 24     | 17         | 66          |

| Computation/Memory | 1.70   | 1.84   | 1.43       | 1.00        |

| DLP Granularity    | 1,8,16 | 1,4,8  | 10         | 9750        |

| (in 128b words)    |        |        |            | (stream)    |

| % Reductions       | 36     | 10     | 28         | 50          |

Table 2.3: DLP characteristics of applications.

Table 2.3 summarizes the DLP characteristics of our applications, except for RayTrace, which has only TLP and ILP.

The first row summarizes the sub-word sizes used by each application. MPGenc and MPGdec

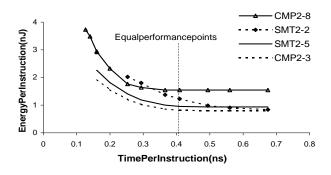

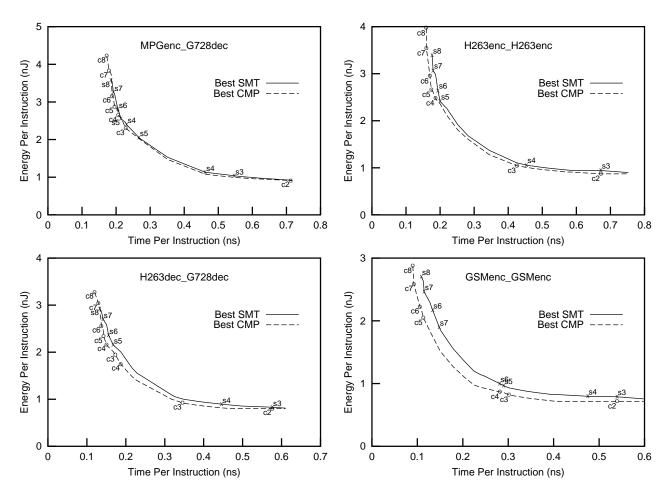

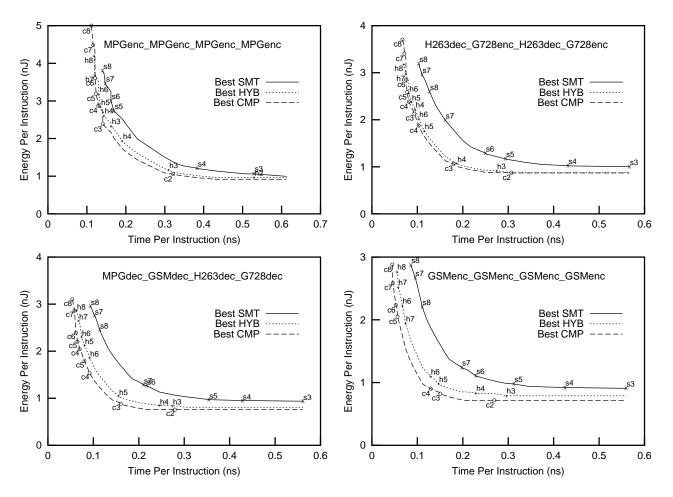

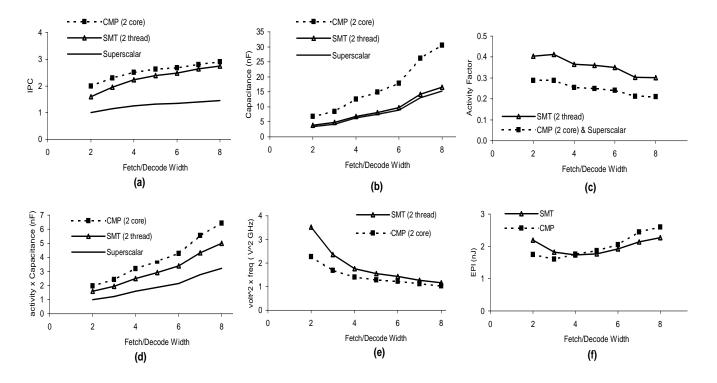

Figure 2.1: Scalability of TLP without SIMD instructions (a) with a perfect 1-cycle memory system, and (b) with realistic memory parameters.