$\bigodot$  2008 Xiaodong Li

#### SOFT ERROR MODELING AND ANALYSIS FOR MICROPROCESSORS

#### BY

#### XIAODONG LI

B.Eng., University of Science and Technology of Beijing, 1997 M.Eng., Institute of Automation, Chinese Academy of Sciences, 2000 M.S., Purdue University, 2002

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2008

Urbana, Illinois

Doctoral Committee:

Professor Sarita V. Adve, Chair Professor Joseph Torrellas Associate Professor Yuanyuan Zhou Assistant Professor Craig Zillas Doctor Jude Rivers, IBM Research

## Abstract

Soft errors are a growing concern for processor reliability. Recent work has motivated architecture level studies of soft errors since the architecture level can mask many raw errors and architectural solutions can exploit workload knowledge. My dissertation focuses on the modeling and analysis of soft error issues at the architecture level.

We start with the widely used method for estimating the architecture level mean time to failure (MTTF) due to soft errors. The method first calculates the failure rate for an architecture level component as the product of its raw error rate and an architecture vulnerability factor (AVF). Next, the method calculates the system failure rate as the sum of the failure rates (SOFR) of all components, and the system MTTF as the reciprocal of this failure rate. Both steps make significant assumptions. We analyze the validity of the two steps using both mathematical analysis and experiments. We find that although the AVF+SOFR method is valid for most current systems under current raw error rates, for some cases it can lead to significant discrepancies. We explore scenarios in which such discrepancies could occur in practice.

To find an alternative model that is not subject to such limitations, we propose a model and tool called SoftArch that does not make the above AVF+SOFR assumptions. SoftArch is based on a probabilistic model of error generation and propagation process in a processor. Our experiments show that SoftArch does not exhibit the discrepancies the AVF+SOFR suffered. We apply SoftArch to an out-of-order processor running SPEC2000 benchmarks. Our results motivate selective and dynamic architecture level soft error protection schemes. Next, as another application, we quantify the impact of technology scaling on the processor soft error rate, taking the architecture level masking and workload characteristics into consideration.

By using the SoftArch tool, we observe that there is much architecture level masking and that the degree of such masking can vary significantly across workloads, individual units, and workload phases. Thus, it is natural to consider the architecture level solutions to take advantage of such variations. In order to do that, one would need reasonably accurate estimate of the amount of masking effect in real time. For most current systems, AVF is an accurate abstraction of the architecture level masking effect. Existing solutions for estimating AVF are often based on offline simulators and usually hard to implement in real processors. In this dissertation, we propose a novel way of estimating AVF online, using simple modifications to the processor. Our method applies to both logic and storage structures on the processor and does not require complex offline calibration for different workloads. We test our method with a widely used simulator from industry for SPEC benchmarks. The results show that the method provides reasonably accurate run-time AVF estimates.

To sum up, this dissertation studies the architecture level soft error modeling and analysis problems. It provides new techniques to examine and take advantage of architecture level soft error behavior. We apply our tool to investigate the impact of technology scaling on soft errors. We also propose an efficient online AVF estimation algorithm.

## Acknowledgements

This dissertation would not have been possible without the support of many people.

First, I would like to express my deep gratitude to my thesis advisor, Prof. Sarita Adve, for her constant guidance and invaluable support through my graduate study. Her insights and attention to detail were instrumental in helping me achieve my academic goals. I also want to thank Dr. Pradip Bose and Dr. Jude Rivers from IBM research, whom I have been fortunate enough to work with during my Ph.D. research. They provided vital industrial perspectives for all my research work.

I am also indebted to the members of my dissertation committee, Prof. Joseph Torrellas, Prof. Craig Zilles, Prof. Yuanyuan Zhou and Dr. Jude Rivers for their critical feedback, especially at my preliminary exam and thesis defense.

I would like to thank the members of the RSIM group, especially Alex Li, and Pradeep Ramachandran, for their important feedback during my practice talks for the prelim and thesis defense.

Finally, I would like to extend my thankfulness to my family for their support throughout all these years. I thank my wife, Jing Liu, for her patience and love that helped me survive the hardest time.

## **Table of Contents**

| Chapte | r 1 Introduction                                                                                                                                                                          | 1        |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1    | Motivation and goal                                                                                                                                                                       | 1        |

| 1.2    | Contributions                                                                                                                                                                             | 1        |

|        | 1.2.1 Limitations of AVF+SOFR                                                                                                                                                             | <b>2</b> |

|        | 1.2.2 SoftArch                                                                                                                                                                            | 2        |

|        | 1.2.3 Online AVF estimation                                                                                                                                                               | 3        |

| 1.3    | Organization                                                                                                                                                                              | 4        |

| Chapte | r 2 Assumptions and limitations of the AVF+SOFR method                                                                                                                                    | <b>5</b> |

| 2.1    | AVF+SOFR method and assumptions                                                                                                                                                           | 7        |

|        | 2.1.1 The AVF step                                                                                                                                                                        | 7        |

|        | 2.1.2 The SOFR step                                                                                                                                                                       | 7        |

|        | 2.1.3 AVF+SOFR assumptions                                                                                                                                                                | 8        |

| 2.2    | AVF+SOFR limitations: an analytical view                                                                                                                                                  | 9        |

|        | 2.2.1 The AVF step: MTTF for an isolated functional or storage unit                                                                                                                       | 10       |

|        | 2.2.2 The SOFR step: MTTF for multiple functional and/or storage units                                                                                                                    | 13       |

|        | 2.2.3 Summary of implications                                                                                                                                                             | 15       |

| 2.3    | AVF+SOFR limitations: an experimental view                                                                                                                                                | 16       |

|        | 2.3.1 Experimental methodology                                                                                                                                                            | 16       |

|        | 2.3.2 Results                                                                                                                                                                             | 21       |

| 2.4    | Summary                                                                                                                                                                                   | 24       |

| Chapte |                                                                                                                                                                                           | 26       |

| 3.1    |                                                                                                                                                                                           | 26       |

| 3.2    | SoftArch details: a model for architecture level MTTF                                                                                                                                     | 27       |

|        | 3.2.1 Error generation model                                                                                                                                                              | 28       |

|        | 1 1 0                                                                                                                                                                                     | 29       |

|        | 3.2.3 Program failure and time to failure                                                                                                                                                 | 32       |

|        | 3.2.4 Determining mean time to failure (MTTF)                                                                                                                                             | 32       |

| 3.3    | Implementation of the SoftArch model                                                                                                                                                      | 34       |

|        | 3.3.1 Integration with timing simulation                                                                                                                                                  | 34       |

|        | 3.3.2 Estimation of $\lambda$                                                                                                                                                             | 35       |

|        | 3.3.3 Estimation of $e_{logic}$                                                                                                                                                           | 36       |

|        | 3.3.4 Tracking basic error set $E_i$ for value $v_i \ldots \ldots$ | 37       |

|        | 3.3.5 Identifying values for program failure                                                                                                                                              | 37       |

| 3.4    | Experiments and results                                                                                                                                                                   | 38       |

|        | 3.4.1 Compare SoftArch to the Monte-Carlo method                                                                                                                                          | 38       |

|                    | 3.4.2 A case study with SoftArch                                           | 38 |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------|----|--|--|--|--|--|

|                    | 3.4.3 Another application of SoftArch: architecture level scaling analysis | 44 |  |  |  |  |  |

| 3.5                | Summary                                                                    | 50 |  |  |  |  |  |

|                    |                                                                            |    |  |  |  |  |  |

| Chapte             |                                                                            | 51 |  |  |  |  |  |

| 4.1                | Introduction                                                               | 51 |  |  |  |  |  |

| 4.2                | AVF estimation algorithm                                                   | 54 |  |  |  |  |  |

|                    | 4.2.1 Overview of the algorithm                                            | 54 |  |  |  |  |  |

|                    | 4.2.2 Determining potential failure                                        | 56 |  |  |  |  |  |

|                    | 4.2.3 Determining $N$ – the number of error injection samples needed       | 57 |  |  |  |  |  |

|                    | 4.2.4 Determining $M$ – the interval between successive error injections   | 59 |  |  |  |  |  |

|                    | 4.2.5 Hardware support and overhead                                        | 61 |  |  |  |  |  |

|                    | 4.2.6 Limitations                                                          | 62 |  |  |  |  |  |

| 4.3                | Experimental methodology                                                   | 63 |  |  |  |  |  |

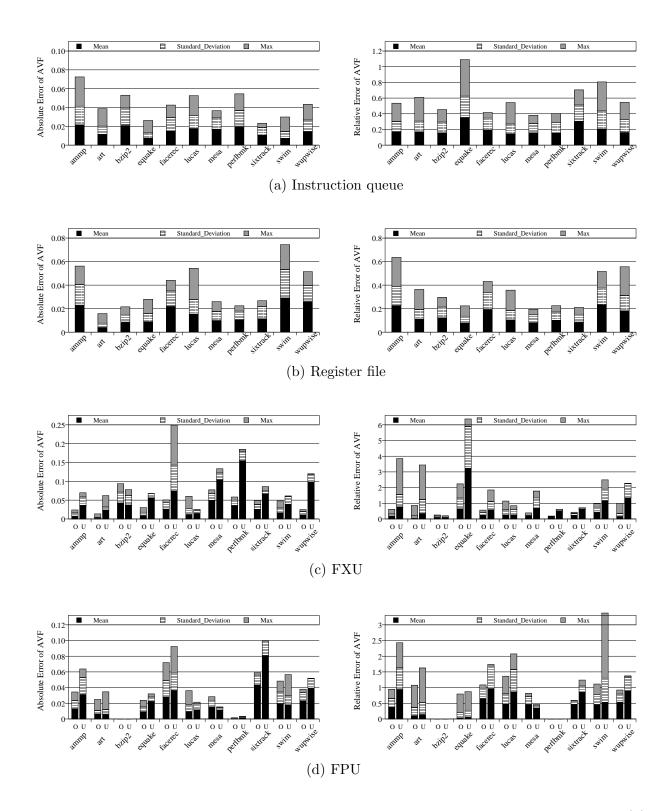

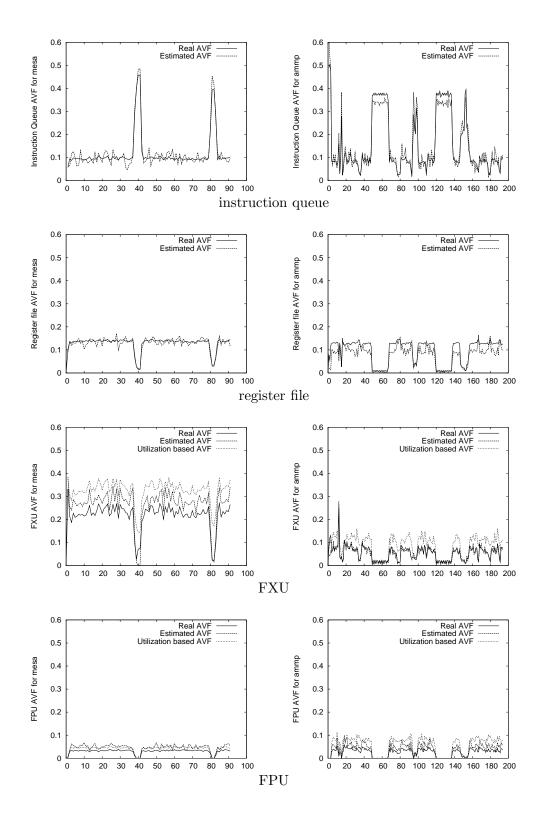

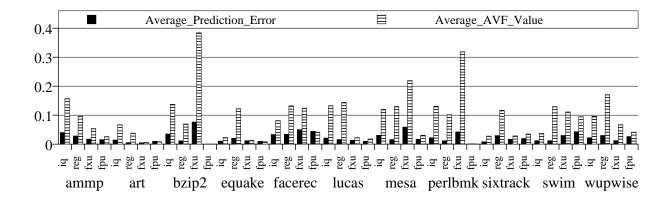

| 4.4                | Results                                                                    | 64 |  |  |  |  |  |

| 4.5                |                                                                            |    |  |  |  |  |  |

|                    |                                                                            |    |  |  |  |  |  |

| Chapte             |                                                                            | 71 |  |  |  |  |  |

| 5.1                | Soft error modeling                                                        | 71 |  |  |  |  |  |

| 5.2                | AVF estimation                                                             | 72 |  |  |  |  |  |

| 5.3                | Soft error protection schemes                                              | 73 |  |  |  |  |  |

| 5.4                | Other related work                                                         | 74 |  |  |  |  |  |

| Chapte             | er 6 Conclusions and future directions                                     | 76 |  |  |  |  |  |

| 6.1                | Conclusions                                                                | 76 |  |  |  |  |  |

| 6.2                | Future directions                                                          | 77 |  |  |  |  |  |

| 0.2                | 6.2.1 Architecture level solution for soft errors                          | 77 |  |  |  |  |  |

|                    | 6.2.1 Arcintecture level solution for solt errors                          | 78 |  |  |  |  |  |

|                    | 0.2.2 Onmed system wide adaptation framework                               | 10 |  |  |  |  |  |

| Refere             | $\mathbf{nces}$                                                            | 80 |  |  |  |  |  |

| Author's Biography |                                                                            |    |  |  |  |  |  |

## Chapter 1

## Introduction

#### 1.1 Motivation and goal

CMOS technology scaling has brought tremendous improvement in performance for semiconductor devices. As we move to sub-100nm lithographies, however, soft errors are emerging as a new challenge in processor design. Soft errors or single event upsets are transient errors caused by high energy particle strikes such as neutrons from cosmic rays [1, 2] and alpha particles from packaging material. Such strikes can flip the bit stored in a storage cell and change the value being computed by a logic element. Although a consensus on exact soft error rates is still lacking, there is a growing concern about the phenomenon.

Recent work has shown that many of the raw errors that occur at the device and circuit level may be masked at the architecture level, potentially motivating lower cost protection mechanisms. For example, Wang et al. report that about 85% of the raw errors are masked at the architecture level [3]. By considering solutions at the architecture level, knowledge of workload behavior can be exploited, leading to potentially more efficient protection solutions (e.g., [3, 4]). These observations motivate the need for comprehensive models and tools to study soft errors at the architecture level and solutions at the architecture level to remedy the problem.

In this dissertation, we focus on the architecture level modeling and analysis of the soft error problem.

#### **1.2** Contributions

This dissertation makes three key contributions.

- 1. Analyzes the assumptions and limitations of the AVF+SOFR method [5].

- 2. Proposes SoftArch, a new architecture level model and tool for modeling and analyzing soft errors at the architecture level [6].

- 3. Proposes a novel method for online estimation of AVF for soft errors [7].

We now discuss each of the contributions in more detail.

#### 1.2.1 Limitations of AVF+SOFR

The first contribution of this dissertation is a detailed analysis of the limitations of the widely used method for estimating MTTF due to soft error – the AVF+SOFR method. First, our work builds a fundamental understanding of the AVF+SOFR method at the architecture level. It explicitly identifies some fundamental assumptions in the AVF+SOFR approach and shows that these assumptions depend on three parameters. We then use both mathematical and experimental techniques to check the validity of the above method across a large design space. We find that the above method is valid for most of the realistic cases under current raw error rates. However, for some combinations of large systems, long running workloads with large phases, and/or high raw error rates, the AVF+SOFR method can lead to significant discrepancies.

#### 1.2.2 SoftArch

In search for an alternative model, we propose SoftArch, to enable analysis of soft errors at the architecture level in modern processors. SoftArch is based on a probabilistic model of error generation and propagation process in a processor. Compared to prior architecture level tools, SoftArch is more comprehensive or faster. What is more important, our experiments show that SoftArch does not need to make the same assumption that AVF+SOFR method does. The MTTF computed by SoftArch has less than 2% error relative to the MTTF value calculated using the Monte-Carlo method for the whole wide design space we have studied.

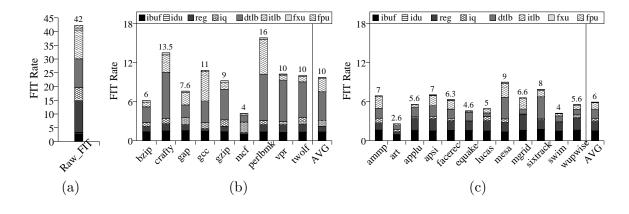

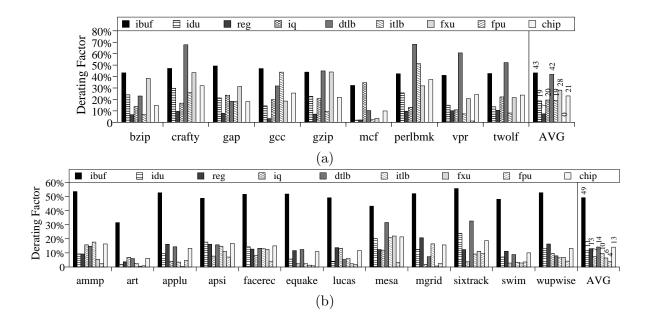

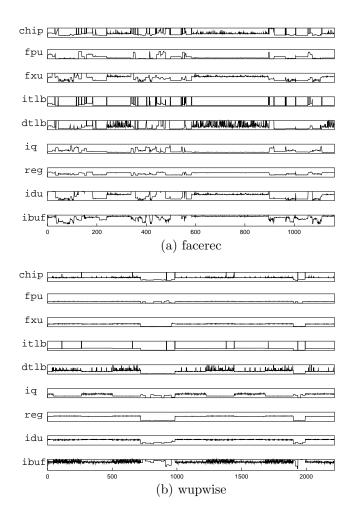

We also use SoftArch to quantify the MTTF of a modern out-of-order processor and the contribution of different structures to the failure rate, for various SPEC benchmarks. Our results are consistent with previous studies. We show that not only is there significant architecture level masking effects, there is substantial inter- and intra-application variation in MTTF or failure rate and substantial application-dependent variation that contributes to the failure rate from different structures. These results motivate selective protection of only the most vulnerable structures and dynamic, application-aware protection schemes.

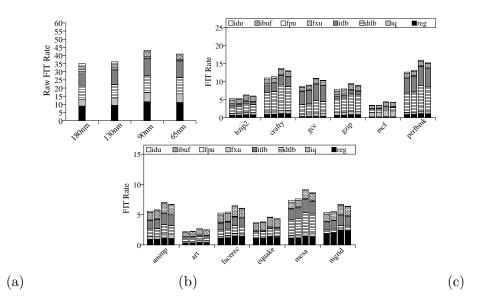

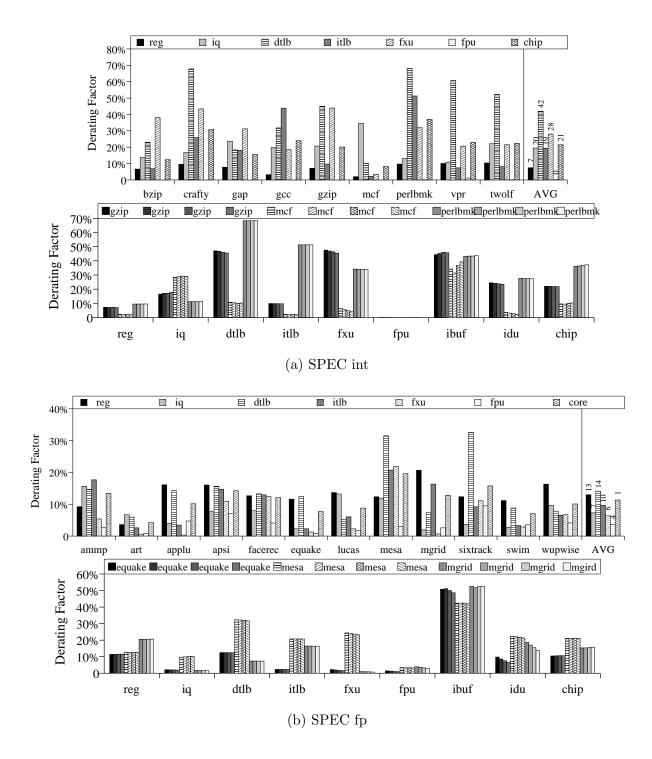

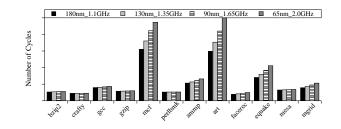

As another application, we apply SoftArch to quantify the impact of technology scaling on the processor soft error rate, taking the architecture level masking effects and workload characteristics into consideration. For our evaluation, we use SoftArch to study the AVF and soft error rate (SER) for different structures in a modern superscalar processor running SPEC2000 benchmarks. We compare the SERs across four different technologies ranging from 180nm to 65nm with the same microarchitecture. We find that with scaling, the AVF for logic structures often decrease, the AVF for storage elements remains roughly unchanged, and the MTTF for the full processor roughly follows the trend for the raw SER of storage structures (i.e., the MTTF decreases from 180nm to 90nm and increases from 90nm to 65nm.) This study assumes the number of transistors on the chip stays the same.

#### 1.2.3 Online AVF estimation

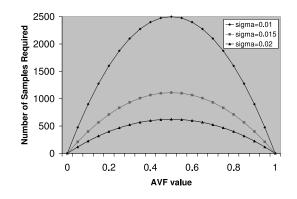

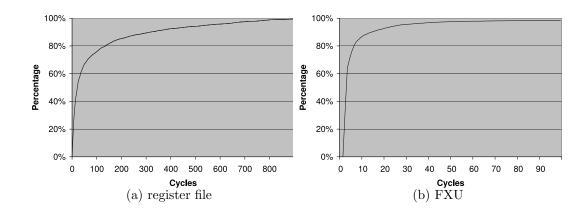

Using SoftArch, we find that there is much architecture level masking and that the degree of such masking can vary significantly across workloads and also individual workload phases. This provides opportunities for an architecture level solution to take advantage of the application behavior variation. For that to happen, it is important to be able to accurately estimate the masking effect which is captured by the architecture vulnerability factor (AVF) for most current systems. Existing solutions for estimating AVF are often based on off-line simulators and are usually hard to implement in real processors. This dissertation proposes a novel way of estimating AVF on-line while the program is running. We propose some simple hardware modifications for the processor and use an algorithm to effectively estimate AVF. It is a general method that applies to both logic and storage units on the processor. Compared to previous methods for estimating AVF, our method does not require offline simulation with simulators, nor does it require calibration for different workloads. We test our method with SoftArch coupled to a widely used simulator from industry and SPEC benchmarks. The results show that our method provides accurate run-time AVF estimates.

#### 1.3 Organization

The rest of the dissertation are organized as follows. Chapter 2 analyzes the current state-of-the-art AVF+SOFR soft error modeling method. Chapter 3 proposes SoftArch, an architecture level model and tool to analyze soft errors at the architecture level. Chapter 4 proposes a new efficient on-line AVF estimation method. Chapter 5 discusses related work and Chapter 6 presents the conclusions of this dissertation and possible avenues of future work.

### Chapter 2

# Assumptions and limitations of the AVF+SOFR method

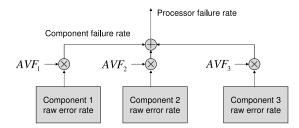

The AVF+SOFR method has been widely used in estimating processor MTTF values. The methodology computes MTTF using two simple steps [8], illustrated in Figure 2.1. The **AVF step** calculates the failure rate of each individual processor *component* (e.g., ALU, register file, issue queue) as the product of its raw failure rate and a factor that accounts for architecture level masking effect. Mukherjee et al. formalize the notion of the architecture level masking effect as the architectural vulnerability factor (AVF) [8] and show how to calculate it for various architectural components [9, 8]. The **SOFR step** calculates the failure rate of the entire processor (or any system) as the Sum Of the Failure Rates (SOFR) of the individual components of the processor or system (as calculated in the AVF step). It calculates the MTTF of the processor (or system) as the reciprocal of its failure rate.

Figure 2.1 The AVF and SOFR steps for MTTF.

Both the AVF and SOFR steps implicitly make certain assumptions about the statistical properties of the underlying error process. While these assumptions, described below, may hold for the raw error process, it is unclear whether they hold for the architecturally masked process. Our goal is to examine the validity of these assumptions underlying the mathematical basis of the AVF and SOFR steps, and the implications of these assumptions for evaluating soft error MTTF for real systems.

Next, we will analyze the assumptions through mathematical analysis and experiments. Our rigorous mathematical methods analyze the limits and value ranges of various parameters within which the AVF+SOFR assumptions hold true. In order to validate the conclusions and quantify the limits, we design simulation-based experiments to explore a wide design space.

We find that the impact of the above assumptions on the MTTF calculation depends on three parameters related to the environment, system, and the workload respectively: (1) the raw error rate of the individual components, (2) the number of components in the system on which SOFR is applied, and (3) the length of the full execution or the longest repeated phase of the workload. Specifically, our evaluations show the following.

- 1. For systems where the individual components have small raw error rates, the total number of components is small, and where the workload consists of repeated executions of a short program, the AVF+SOFR assumptions introduce negligible error. To our knowledge, previously published work using the AVF+SOFR methodology considers systems and workloads that obey the above constraints. This result is by itself significant since it, for the first time, validates the mathematical basis for using the AVF+SOFR methodology.

- 2. Our results show that the AVF+SOFR method can result in large discrepancies in MTTF (up to 100%) for individual components that have large raw error rates (e.g., as would be the case in space or in accelerated tests or with components consisting of many millions of bits) and/or systems that have many components (e.g., large clusters of thousands of processors) and/or long-running workloads with different utilization characteristics over large time windows (e.g., server workloads that run at high utilization in the day but low utilization in the night). This problematic part of the design space is certainly much smaller and less common than the space over which AVF+SOFR is valid; however, it is not negligible and represents several realistic systems. Our results give a note of caution against blind use of the AVF+SOFR method for such systems.

We discuss the AVF+SOFR method and their assumptions in detail in Section 2.1. Section 2.2

and Section 2.3 provide an analytical and an experimental view.

#### 2.1 AVF+SOFR method and assumptions

#### 2.1.1 The AVF step

In a given cycle, only a fraction of the bits in a processor storage component and only some of the logic components will affect the final program output. A raw error event that does not affect these critical bits or logic components has no adverse effect on the program outcome. Mukherjee et al. used the term architecture vulnerability factor (AVF) to express the probability that a visible error (failure) will occur, given a raw error event in a component [8]. The AVF for a hardware component can be calculated as the percentage of time the component contains *Architecturally Correct Execution* (ACE) bits (i.e., the bits that affect the final program output). Thus, for a storage cell, the AVF is the percentage of cycles that this cell contains ACE bits. For a logic structure, the AVF is the percentage of cycles that it processes ACE bits or instructions.

Mukherjee et al. calculate the FIT rate of a processor component as the product of the component's AVF and its raw FIT rate (i.e., the FIT rate of the component if every bit were ACE). Denoting the raw FIT rate of the component as  $\lambda_c$  (also called the raw soft error rate or raw SER) and its AVF as  $AVF_c$ , they derive the MTTF of the component as:

$$MTTF_c = \frac{1}{\lambda_c \cdot AVF_c} \tag{2.1}$$

We show in Section 2.2.1 that an assumption underlying the above equation is that the time to failure for a program is uniformly distributed over the program. We explore the cases where this assumption is and is not true to assess the validity of the AVF step.

#### 2.1.2 The SOFR step

Sum of failure rates (SOFR) is an industry standard model for combining failure rates of individual processor (or system) components to give the failure rate and MTTF of the entire processor (or system). Let the system contain k components with failure rate of component i as  $FailureRate_i$  (which is assumed to be the reciprocal of the MTTF of component i or  $1/MTTF_i$ ). The SOFR

model calculates the failure rate  $(FailureRate_{sys})$  and the MTTF  $(MTTF_{sys})$  of the system as:

$$FailureRate_{sys} = \sum_{i=1}^{k} FailureRate_i = \sum_{i=1}^{k} \frac{1}{MTTF_i}$$

(2.2)

$$MTTF_{sys} = \frac{1}{FailureRate_{sys}}$$

(2.3)

The SOFR model makes two major assumptions [10]. First, it assumes that each component has a constant failure rate (i.e., exponentially distributed time to failure) and the failures for different components are independent of each other. Section 2.2.2 shows that architectural masking may violate this assumption in some cases. Second, the SOFR model assumes a series failure system; i.e., the first instance of a component failure causes the entire processor to fail. This assumption holds if there is no redundancy in the system. Since our focus is on the impact of program-dependent architectural masking on the statistical properties of the failure process, we continue to make this assumption as well and focus only on the first assumption.

#### 2.1.3 AVF+SOFR assumptions

A key assumption behind the AVF step is that the probability of failure due to a soft error in a given component is uniform across a program's execution. This allows a single AVF value to be used to derate the raw error rate of a component. The uniformity assumption is reasonable for raw error events since the probability of a high energy particle strike is no different at different points in the program's execution for most realistic scenarios. However, it is unclear that the assumption holds after incorporating architectural masking. Similarly, a well-documented assumption for the SOFR step is that the time to failure for a given component follows an exponential distribution. Again, the assumption is reasonable and widely accepted for raw error events, but it is unclear that it holds for failures after architectural masking.

Thus, both the AVF and SOFR steps make assumptions about the error process that may be considered questionable, once architectural masking effects are taken into account. The question we address is: Under what conditions (if any) does the violation of the above AVF+SOFR assumptions introduce significant errors in the calculation of the MTTF?

#### 2.2 AVF+SOFR limitations: an analytical view

This section uses mathematical analysis to understand the limits of the basic assumptions underlying the AVF+SOFR methodology for estimating MTTF for soft errors. Later sections back these results with detailed Monte-Carlo simulations for actual workloads.

Our analysis makes two assumptions that are also made by the AVF+SOFR methodology.

(1) Inter-arrival times for raw errors in a component are independent and exponentially distributed with density function  $\lambda e^{-\lambda t}$ . It is reasonable to assume that the time to the next high energy particle strike is independent of the previous strike and is exponentially distributed (the process is memoryless). In practice, there is some device- and circuit-level masking, which could possibly render the raw error process that is subject to architectural masking as non-exponential. In our experiments, however, we do not have this low-level masking information available; we therefore assume the best case for the AVF+SOFR methodology – that the inter-arrival time for raw errors before any architectural masking is an exponential process with density function  $\lambda e^{-\lambda t}$ . We refer to  $\lambda$  as the raw error rate.

(2) The workload runs in an infinite loop with similar iterations of length L. This work considers the effect of real application workloads. For a workload that runs for a finite time, there is a possibility that no failure occurs during its execution. For a meaningful interpretation of MTTF for a system running such a workload, we assume that the workload runs repeatedly in a loop until the first failure. All iterations of this loop are identical and each represents a single invocation of the original workload. We refer to the size of this loop iteration as L. Workloads that are naturally infinite also run in a loop. We assume that such a workload also consists of identical iterations, each of size L. This assumption is trivially satisfied since L can potentially be infinite. (All the prior work on AVF+SOFR has been in the context of finite workloads.)

We additionally assume that program failure occurs if a raw error is not masked. Although the time to failure and the time to the next raw error event are continuous random variables, for convenience, we often consider time in units of processor cycles below (for architectural masking, for a given cycle, all raw error events during any part of the cycle are either masked or not masked).

Figure 2.2 Sequence of raw error events.  $t_i$  is the time between two raw error events and is exponentially distributed. X is a random variable representing the time to the first raw error event that is not masked and leads to program failure. The figure shows a case where  $X = t_1 + t_2 + t_3$ .

#### 2.2.1 The AVF step: MTTF for an isolated functional or storage unit

The AVF step computes the MTTF of a single component of the processor using equation 2.1. We examine the validity of this step by deriving the MTTF of a given component from first principles.

Figure 2.2 illustrates a sequence of raw error events with inter-arrival times of  $t_1, t_2, ..., t_n, ...$ Each of these times is an instance of a random variable, say T, with exponential density function  $\lambda e^{-\lambda t}$ . Each raw error has some probability of being masked. Failure occurs at the first raw error that is not masked.

Let X be the random variable that denotes the time to failure. Then  $X = t_1 + t_2 + ... + t_k$  if the first k - 1 raw errors are masked and the kth raw error is not masked. Thus,  $X = \sum_{i=1}^{K} t_i$ , where K is a random variable such that K = k denotes the event that the first k - 1 raw errors are masked and the kth raw error is not masked.

Now the MTTF of the component is simply the expected value of X, E(X). Using a standard result for the expectation of a sum of random variables [11], it follows that: MTTF = E(X) = E(K)E(T). We know that  $E(T) = \frac{1}{\lambda}$  (this would be the MTTF if there were no architectural masking and every raw error resulted in failure). Thus,

$$MTTF = E(K)\frac{1}{\lambda} \tag{2.4}$$

Comparing with equation 2.1, to validate the AVF step, we would need to show that  $E(K) = \frac{1}{AVF}$  for all cases. However, E(K) depends on the workload characteristics and the raw error rate  $\lambda$ , and, in general, cannot be analytically derived. Nevertheless, with certain assumptions, we show that we can derive E(K) to be 1/AVF, validating the AVF step for cases where the assumptions hold. We then show counter-examples where these assumptions do not hold, and the MTTF derived

from first principles is significantly different from the MTTF derived from the AVF equation 2.1.

#### **AVF** is valid when $L \cdot \lambda \to 0$

We first show that if the product of the raw error rate and the program loop size is very small, then  $E(K) = \frac{1}{AVF}$  (and so the AVF equation holds). Below we show that in this case, any of the L cycles in the program loop are equally vulnerable to a raw error event occurrence. From this, it will follow that the expected value of K (i.e., the count of the first raw error event that is not masked) is the same as 1/AVF.

Let T be the cycle count at which the next raw error event occurs. Then, without loss of generality, T mod L is the cycle count for this event relative to the start of the loop iteration. Appendix A of an extended version technical report [12] shows that if  $L \cdot \lambda \to 0$ , the random variable T mod L follows a uniform distribution over [0, L]. In other words, for very small  $L \cdot \lambda$ , any of the L cycles of program execution are equally vulnerable to a raw error event occurrence.

Thus, the probability that the next raw error event occurs at cycle *i* (relative to the start of the loop iteration) is 1/L. Let  $p_i$  be the probability that a raw error event that occurs at cycle *i* (relative to the start of the loop iteration) is masked ( $p_i$  is 0 or 1 for a given program execution). Therefore, the probability that the next raw error event is masked is  $\sum_{i=1}^{L} \frac{1}{L} \cdot p_i$ . This value is a constant that we denote by M.

Now to calculate E(K), we first calculate  $P\{K=k\}$ . This is the probability that the first k-1 raw error events are masked and the kth raw error event is not masked. Since raw error events are independent, it follows that  $P\{K=k\} = M^{k-1}(1-M)$ . That is, K is a geometrically distributed random variable and so E(K) = 1/(1-M). Thus, we just need to show that 1-M is the same as the AVF.

(1-M) can be expressed as  $\sum_{i=1}^{L} \frac{1-p_i}{L}$ .  $1-p_i$  is the probability that a raw error event at cycle i will not be masked and will cause failure. 1-M is therefore the average of this probability over the entire program length. This is exactly the definition of AVF. Thus, we have shown that the AVF equation 2.1 is valid when  $L \cdot \lambda \to 0$ .

#### AVF is not valid for some values of $\lambda$ and L

In this section, we construct a simple (synthetic) program that serves as a counter-example to show that the assumptions behind the AVF step do not always hold.

Consider a program with an infinite loop with iteration size L, such that the considered system component is active for the first A cycles and is idle for the remaining A + 1 to L cycles of the iteration. As before, let X be the random variable denoting the time to failure for the component running the above program. Let T be the random variable denoting the time to the first raw error event. If T is in cycles [0, A], [L, L + A], ..., then the component is active and the time to failure is simply the value of T. Otherwise, the raw error occurs in an idle period, say, of iteration k, and it is masked. Further, any raw errors until the next active period (i.e., until cycle kL) will also be masked.

As seen at cycle kL, the distribution for the time to the next raw error event (starting from kL) is the same as that starting from time 0. This is due to the memoryless property of the exponential distribution.<sup>1</sup> Further, as seen from kL, the masking process is also the same as at time 0, since all iterations are identical. Thus, given that there is no failure until cycle kL, the expected time to failure from cycle kL is again E(X).

It follows that given that the first raw error event occurs in the idle period of the *kth* iteration, the expected time to failure is kL + E(X). Now using a standard result for conditional expectation [11], we get the following:

$$\begin{split} E(X) &= E(E(X|T)) = \int_0^\infty E_{X|T}(t) \cdot f_T(t) dt \\ &= \int_0^A \lambda e^{-\lambda t} t dt + \int_A^L \lambda e^{-\lambda t} (L + E(X)) dt + \\ &\int_L^{L+A} \lambda e^{-\lambda t} t dt + \int_{L+A}^{2L} \lambda e^{-\lambda t} (2L + E(X)) dt ... \end{split}$$

The above equation has the following closed form solution (Appendix A of [12]), giving the MTTF of the component from first principles:

$$\begin{split} E(X) &= \frac{1 - e^{-\lambda L}}{1 - e^{-\lambda A}} \cdot \left(\frac{L e^{-\lambda L}}{(1 - e^{-\lambda L})^2} - \frac{L e^{-\lambda A} e^{-\lambda L}}{(1 - e^{-\lambda L})^2} - \frac{A e^{-\lambda A}}{(1 - e^{-\lambda L})} + \frac{1}{\lambda} \frac{(1 - e^{-\lambda A})}{(1 - e^{-\lambda L})} + L \frac{e^{-\lambda A} - e^{-\lambda L}}{(1 - e^{-\lambda L})^2} \right) \end{split}$$

<sup>&</sup>lt;sup>1</sup>Recall that for an exponential distribution,  $P(T < t + \Delta t | T > t) = \frac{(e^{-\lambda t} - e^{-\lambda(t+\Delta t)})}{e^{-\lambda t}} = 1 - e^{-\lambda \Delta t}$ . That is, given that a raw error has not occurred at time t, the probability that the error will occur within some time  $\Delta t$  after t is the same as that of it occurring within  $\Delta t$  after time 0.

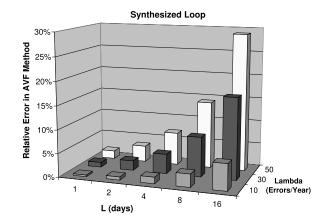

Figure 2.3 The relative error in the AVF step applied to a large 100MB cache running a loop with iteration size of L days with each iteration busy for L/2 days and idle for the rest. Lambda is the raw error rate of the entire cache (the smallest value represents 0.001 FIT per bit).

The AVF for our program is  $\frac{A}{L}$ ; therefore, the MTTF according to the AVF method is:

$$E_{AVF}(X) = \frac{L}{A} \cdot \frac{1}{\lambda}$$

Now we can calculate the relative difference between the MTTF from first principles and from the AVF method as:

$$\frac{|E_{AVF}(X) - E(X)|}{E(X)}$$

When  $\lambda L$  is very small, we can show that the two MTTFs converge to the same value. For other cases, there can be a significant difference. Figure 2.3 shows the difference between the two MTTF values for a 100MB cache for different values of L and  $\lambda$ . We vary L from 1 to 16 days, setting A as L/2 in each case. We start with  $\lambda$  at  $10^{-8}$  errors/year per bit (0.001 FIT/bit) [6] which translates to 10 errors/year for the full cache. We additionally show results for  $\lambda$  of 3 and 5 times this value to represent changes in technology and altitude. Although the errors are small for the baseline (smallest) value of  $\lambda$ , they can be significant for higher values. Later sections perform a more systematic experimental exploration of the full parameter space.

#### 2.2.2 The SOFR step: MTTF for multiple functional and/or storage units

The SOFR step derives the MTTF of a system using the MTTFs of its individual components, as shown in equations 2.2 and 2.3. As discussed in Section 2.1.2, it assumes that for each component, the time to failure follows an exponential distribution with a constant failure rate (in conjunction with the AVF step, this rate is the product of the component's raw error rate and AVF). We next explore the validity of this assumption, given that each component sees significant architectural masking.

Again, the validity of the assumption depends on the values of the component's raw error rate  $\lambda$  and the program loop size L. Sections 2.2.2 and 2.2.2 respectively discuss cases for which the assumption is and is not valid.

#### **SOFR** is valid when $L \cdot \lambda \to 0$

We show that if  $L \cdot \lambda \to 0$  for a component, then the time to failure, X, for that component is exponentially distributed with rate parameter  $\lambda \cdot AVF$ .

Section 2.2.1 showed that in this case,  $X = \sum_{i=1}^{K} t_i$ , where K follows a geometric distribution with mean 1/AVF and the  $t_i$ 's are exponentially distributed with rate  $\lambda$ . We can calculate the density function of X as follows:

$$f_X(x) = \lim_{\Delta x \to 0} \frac{P(x < X < x + \Delta x)}{\Delta x}$$

$$= \lim_{\Delta x \to 0} \sum_{i=1}^{\infty} \frac{P(x < X < x + \Delta x | K=i) P(K=i)}{\Delta x}$$

where  $P(x < X < x + \Delta x | K=k) = P(x < \sum_{j=1}^k t_j < x + \Delta x).$

$\sum_{j=1}^{k} t_j$  is the sum of several independent exponentially distributed random variables with rate  $\lambda$ . Such a sum follows the Erlang-n distribution which has the probability density function of  $\frac{\lambda(\lambda x)^{n-1}}{(n-1)!}e^{-\lambda x}$  [10]. Thus,

$$f_X(x) = \sum_{i=1}^{\infty} \left( (1 - AVF)^{i-1} (AVF) \frac{\lambda(\lambda x)^{i-1}}{(i-1)!} e^{-\lambda x} \right)$$

$$= (AVF)\lambda e^{-\lambda x} \sum_{i=1}^{\infty} \frac{((1 - AVF)\lambda x)^{i-1}}{(i-1)!}$$

$$= \lambda (AVF) e^{-\lambda(AVF)x}$$

This is an exponential distribution with rate  $\lambda \cdot AVF$ . This validates the assumption for the SOFR step for the case when  $\lambda \cdot L$  is small.

#### The general case for $\lambda$ and L values

In general, it is difficult to analytically characterize the time to failure distribution function for real (or even synthetic) programs after architectural masking. In this section, to demonstrate a mathematical basis, we choose a distribution that is "close" to exponential (and mathematically tractable) and determine the validity of using SOFR on that distribution.

We choose the following probability density function for the time to failure (after architectural masking) for a component.

$$f_X(x) = \begin{cases} \frac{2}{\sqrt{\pi}} e^{-x^2} & x \in [0, \infty] \\ 0 & \text{elsewhere} \end{cases}$$

The cumulative distribution function (CDF) of X is  $F_X(x) = \frac{2}{\sqrt{\pi}} \int_0^x e^{-t^2} dt, x \in [0, \infty].$ It follows that the MTTF of the component is  $E(X) = \frac{2}{\sqrt{\pi}} \int_0^\infty x e^{-x^2} dx = \frac{1}{\sqrt{\pi}}.$

Assume a system with N such identical components where  $X_i$  denotes the time to failure for component *i*. Since we assume series failure, it follows that the time to failure of the system, Y, is  $\min(X_1, X_2, ..., X_N)$ .

The CDF of Y is  $F_Y(y) = 1 - (1 - F_X(y))^N$ .

The PDF is  $f_Y(y) = \frac{dF_Y(y)}{dy} = N * (1 - F_X(y))^{N-1} * f_X(y)$

The MTTF of the system is  $E(Y) = \int_0^\infty f_Y(y) y dy$

The above integration cannot be calculated analytically. We solve it numerically using a software package to derive the real MTTF for N from 2 to 32.

The SOFR step calculates the MTTF of the system using Equations 2.2 and 2.3. For the component MTTFs used in the equations, we use the real MTTF derived above  $(\frac{1}{\sqrt{\pi}})$ :

$$MTTF_{sofr} = \frac{1}{\sum_{i=1}^{N} \sqrt{\pi}} = \frac{1}{N\sqrt{\pi}}$$

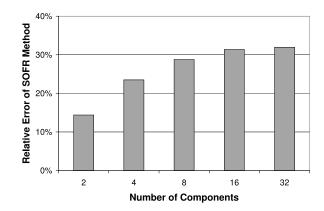

Figure 2.4 shows the error in  $MTTF_{sofr}$  relative to the MTTF derived from first principles. We see that the error grows from 15% for a system with two components to about 32% for a system with 32 components.

#### 2.2.3 Summary of implications

Our mathematical analysis so far provides intuition for when the AVF+SOFR method works. The AVF step averages the "utilization" of a component over the whole program. It therefore makes

Figure 2.4 The relative error introduced by the SOFR step for a synthesized example. the implicit assumption that every point of the program will have uniform probability of being hit by a soft error. The SOFR step assumes that the time to failure for each individual component follows the exponential distribution. Our analysis shows that the above assumptions are valid when  $\lambda \cdot L \rightarrow 0$ . However, in the general case, these assumptions may not hold. We show mathematically tractable synthetic examples to illustrate a few such cases. The next sections provide a more systematic experimental exploration of the parameter space to assess the extent of the errors due to these assumptions.

#### 2.3 AVF+SOFR limitations: an experimental view

In this section, we show that significant discrepancies can arise in many realistic scenarios using experiments with SPEC benchmarks.

#### 2.3.1 Experimental methodology

This section describes the methodology for our experimental analysis of the assumptions of the AVF and SOFR steps. For each step, we first evaluate the assumptions for single processor systems common today running SPEC CPU2000 applications, and using detailed simulation to determine architectural masking. We then take a broader view, and evaluate the assumptions for a large design space, including large clusters of processors and a broader range of (synthesized) workloads, but with less detailed simulation of architectural masking.

For both cases, we first generate a *masking trace* that indicates, for each system component, whether a raw error in a given cycle would be masked for the evaluated system and workload.

| Base Processor Parameters            |                                                      |  |  |  |  |  |  |

|--------------------------------------|------------------------------------------------------|--|--|--|--|--|--|

| Processor frequency                  | 2.0 GHz                                              |  |  |  |  |  |  |

| Fetch/finish rate                    | 8 per cycle                                          |  |  |  |  |  |  |

| Retirement rate                      | 1 dispatch-group $(=5, \max)$ per cycle              |  |  |  |  |  |  |

| Functional units                     | 2 integer, 2 FP, 2 load-store, 1 branch              |  |  |  |  |  |  |

| Integer FU latencies                 | 1/4/35 add/multiply/divide                           |  |  |  |  |  |  |

| FP FU latencies                      | 5 default, 28 divide (pipelined)                     |  |  |  |  |  |  |

| Reorder buffer size                  | 150 entries                                          |  |  |  |  |  |  |

| Register file size                   | 256 entries (80 integer, 72 FP, and various control) |  |  |  |  |  |  |

| Memory queue size                    | 32 entries                                           |  |  |  |  |  |  |

| iTLB                                 | 128 entries                                          |  |  |  |  |  |  |

| dTLB                                 | 128 entries                                          |  |  |  |  |  |  |

| Base Memory Hierarchy Parameters     |                                                      |  |  |  |  |  |  |

| L1 Dcache                            | 32KB, 2-way, 128-byte line                           |  |  |  |  |  |  |

| L1 Icache                            | 64KB, 1-way, 128-byte line                           |  |  |  |  |  |  |

| L2 (Unified)                         | 1MB, 4-way, 128-byte line                            |  |  |  |  |  |  |

| Base Contentionless Memory Latencies |                                                      |  |  |  |  |  |  |

| L1 Latency                           | 1 cycles                                             |  |  |  |  |  |  |

| L2 Latency                           | 10 cycles                                            |  |  |  |  |  |  |

| Main memory Latency                  | 77 cycles                                            |  |  |  |  |  |  |

Table 2.1 Base POWER4-like processor configuration.

To calculate the real MTTF of the system (without the AVF+SOFR assumptions), we use the Monte Carlo technique to model the raw error process, apply the masking trace to the process, and determine the MTTF of the modeled system.

#### Today's uniprocessors running SPEC

To determine the impact of architectural masking in a modern processor, we study an out-oforder 8-way superscalar processor (Table 2.1) running programs from the SPEC CPU2000 suite (9 integer and 12 floating point benchmarks). To generate the masking trace, we use Turandot [13], a detailed trace-driven microarchitecture level timing simulator. We simulate an instruction trace of 100 million instructions for each SPEC benchmark running on the above processor configuration.

We choose four processor components to study the impact of architecture masking: the integer, floating point, and instruction decode units, and the 256 entry register file, with raw error rates of  $2.3 \times 10^{-6}$ ,  $4.5 \times 10^{-6}$ ,  $3.3 \times 10^{-6}$ , and  $1.0 \times 10^{-4}$  errors/year respectively ( $10^{-8}$  errors/year = 0.001 FIT). Li et al. [6] derived these error rates using published device error rates for current technology [14] and estimates of the number of devices of different types in different components [6].

For the integer, floating point, and instruction decode units, we assume that a raw error is masked in a cycle if the unit is not processing an instruction in that cycle (i.e., the unit is not busy). If the unit is busy processing an instruction, then for simplicity, we conservatively assume that the error is not masked and will lead to failure. For the register file, we assume that the raw error strikes happen on each register with equal probability and error in a given register is masked if the register contains a value that will never be read in the future. If the register's value will be read, we conservatively assume the error is not masked and will lead to failure. Our assumptions of when an error is not masked are conservative since it is possible that an error in an active unit or in a register value that will be read may not affect the eventual result of the program. We did not perform a more sophisticated analysis to more precisely determine when an error is masked because such an analysis is orthogonal to the point of this dissertation and beyond the scope of this work.

Our detailed Turandot simulation produces a masking trace for each simulated SPEC application. The trace contains information on whether a raw error in a given cycle in one of the four considered processor components will or will not be masked.

#### Broader design space exploration

We also explore a broad design space for the AVF and SOFR steps. We consider a variety of systems consisting of various numbers of components, operating in various environments, with different raw error rates, and running different workloads. We use the term *system* to include a single processor (either a full processor or only a part of it) or a large cluster of thousands of processors. A *component* of a system is the smallest granularity at which the analysis for architectural masking is applied. Specifically, the AVF is calculated at the granularity of a component; the SOFR step then aggregates the information from the different components to give the MTTF for the entire system. In our SOFR experiments, we use component MTTFs obtained from the Monte Carlo method; therefore, the error reported is only that caused by the SOFR step.

Based on our analysis in Section 2.2, the key parameters affecting the AVF and SOFR steps are the raw error rate of the different components of the processor (or system), the number of components in the system (only for SOFR), and the program loop size or workload. The following discusses the space we explore for each of these important parameters. Table 2.2 summarizes this space.

**Component raw error rate.** The component raw error rate depends on the number of devices

| Dimension | Value    |          |          |          |          |  |  |

|-----------|----------|----------|----------|----------|----------|--|--|

| N         | $10^{5}$ | $10^{6}$ | $10^{7}$ | $10^{8}$ | $10^{9}$ |  |  |

| S         | 1        | 5        | 100      | 2000     | 5000     |  |  |

| C         | 2        | 8        | 5000     | 50000    | 500000   |  |  |

| Workload  | SPEC fp  | SPEC int | day      | week     | combined |  |  |

Table 2.2 The design space explored. N = number of elements (e.g., bits) in a component; S = scaling factor for the baseline raw error rate of an element (depends on technology and altitude); and <math>C = number of components in the system (e.g., processors in a cluster).

or elements (bits of on-chip storage or logic elements such as gates) in the component and the raw error rate per element. We denote the number of elements in a component as N. N can be as large as  $10^9$  for large cache structures or if we consider the entire processor as one component in a large cluster of multiple processors. To keep the design space exploration tractable, without loss of generality, we assume that all N elements have the same raw error rate.

We also explore different values for the raw error rate per element. Under current technology, the terrestrial raw error rate per bit for on-chip storage is about  $10^{-8}$  errors/year (0.001 FIT), which we refer to as the baseline raw error rate. To account for changes in the raw error rate due to technology scaling and at high altitudes, we introduce a parameter S that we use to scale the above baseline rate. We use scaling factors of 1, 5, 100, 2,000, and 5,000 in our analysis. The larger factors correspond to systems running in airplanes flying at a high altitude and for systems in outer space because of strong radiation at those heights [2]. Test systems using accelerated conditions are also subject to high raw error rates.

The raw error rate for a given component is determined as the product of N, S, and the above baseline raw error rate (Table 2.2).

Number of components: We denote the number of components in the system as C. We study a wide range of values for C, ranging from 2 to 500,000. The larger numbers represent large cluster systems with C components (each of which may be a full processor or a microarchitectural component within a processor, depending on the granularity at which AVF is collected).

Workload and generation of the masking traces: We evaluate all systems in the broad design space with the SPEC CPU2000 benchmarks mentioned in Section 2.3.1. However, these are short programs (small loop iteration size L). Many real world workloads show large differences in behavior over long time scales (large L) that are difficult to capture with the SPEC benchmarks.

In an attempt to simulate some of the behaviors of real world applications, we construct three synthetic applications. The first (called day) is a continuous loop where the loop iteration size is set to 24 hours. The loop is busy during the day (half the time) and idle at night. The second (called *week*) is a loop with iteration size one week. It is busy during the five business days of the week and idle for the weekend. The third (called *combined*) concatenates two SPEC benchmarks in a loop with iteration size of 24 hours. The first half of the iteration runs one benchmark and the second half runs the other benchmark.

For a system with multiple processors, we assume all processors run the same workload. Additionally, for the synthesized workloads, we assume that a component is a full processor; e.g., C=2implies a 2 processor system. We assume that each processor masks raw errors only during the idle portion of the workload (e.g., night time for the day workload). For the SPEC workloads, we again assume that each component is a full processor (running the same benchmark). For the masking trace, we use the SPEC masking traces for three units in each processor (integer, floating point, and instruction decode) – we apply these three traces to the corresponding units simultaneously to determine whether there is a processor-level failure.

#### Monte carlo simulation

To calculate the real MTTF, we perform Monte Carlo simulation where we do the following for each trial. For each component in the modeled system, we generate a value from an exponential distribution with rate specified by the modeled system (Table 2.2). This value gives the arrival time of the next raw error event for the component. We use the masking trace of the workload to determine whether a raw error at that time would be masked. If it is masked, we generate a new raw error event from an independent exponential distribution for that component and repeat. If it is not masked, we consider the component failed. The component that is earliest to fail gives the time to failure of the system for this trial. We run a total of 1,000,000 trials and report the average of the time to failure as the MTTF of the modeled system/workload configuration.

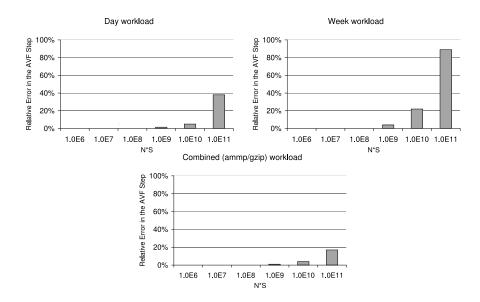

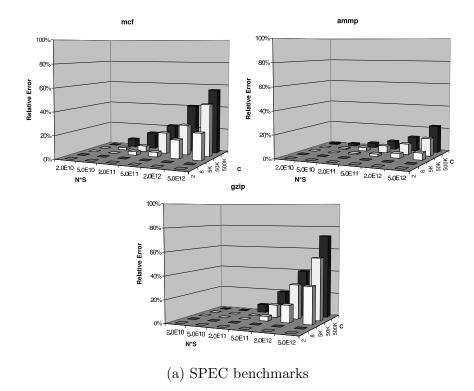

Figure 2.5 Error in MTTF from the AVF step relative to the Monte Carlo method for the synthesized workloads for representative values of  $N \times S$  (# bits in the component  $\times$  scaling factor for baseline raw error rate).

#### 2.3.2 Results

#### AVF and SOFR with Today's Uniprocessors Running SPEC

We first evaluated the discrepancy between the Monte Carlo MTTF and the MTTF using the AVF and SOFR steps for today's uniprocessors running SPEC (as described in Section 2.3.1). We found that the MTTF from the AVF step matched the Monte Carlo MTTF very well for each of the four processor components and each benchmark (< 0.5% discrepancy for all cases). Similarly, the processor MTTF calculated using the SOFR step also matched the Monte Carlo MTTF very well.

Thus, for single processor systems with a small number of small components running SPEC benchmarks, the AVF+SOFR method works very well. We note that in prior work, the method has been applied primarily in this context. These results are consistent with our mathematical analysis. The loop size L for the SPEC benchmarks and the component raw error rates used here are small; therefore, from Sections 2.2.1 and 2.2.2, we expect that the AVF and SOFR assumptions would be valid.

#### **AVF:** A Broad Design Space View

For the design space described in Table 2.2, we computed the component MTTF using the Monte Carlo and AVF methods as described in Section 2.3.1. Note that since the AVF step is applicable to only a single component, C = 1 for all experiments in this section. Further, for a given workload, since only the product of N and S matters, we report relative error in the AVF step as a function of different values of  $N \times S$ .

We found that for each SPEC benchmark, the AVF step works well for all N and S values studied (relative error < 0.5%). However, for the longer running synthesized workloads, we observe significant discrepancy when  $N \times S$  is large (i.e., component raw error rate is large). Figure 2.5 shows the error in the AVF MTTF relative to the Monte Carlo MTTF for representative values of  $N \times S$  for the three synthesized workloads. In all three cases, for  $N \times S \ge 10^9$ , the AVF step sees significant errors (up to 90%). This high value of  $N \times S$  may occur when the AVF step is applied to either large components (e.g., a 125MB cache with  $N = 10^9$  bits), or when the component size is moderate but the raw error rate per element (bit) is high (e.g., S = 1000 because of high radiation at high altitudes).

Our experiments show both positive and negative errors, depending on the workload. Thus, AVF may either over- or under-estimate MTTF in practice.

Again, the above observations match well with our theoretical analysis in Section 2.2.1. Thus, for SPEC like benchmarks that run for a short time, it is safe to use the AVF step to calculate the MTTF of a component. However, the AVF step must be applied carefully when using a workload with large variations over large time scales coupled with either a large component or a large perelement raw error rate for the component.

#### SOFR: A Broad Design Space View

Figures 2.6(a) and (b) report the error in the SOFR step relative to the Monte Carlo method for three representative SPEC benchmarks and the three synthesized benchmarks respectively. For each case, the error is reported for representative values of C and  $N \times S$  covered by the design space in Table 2.2.

Focusing on the SPEC workloads (Figure 2.6(a)), we see that the SOFR step is accurate for

(b) Synthesized benchmarks

Figure 2.6 Error in MTTF from the SOFR step relative to the Monte Carlo method for representative values of C (# components) and  $N \times S$  (bits per component × scaling factor for baseline raw error rate) for (a) SPEC and (b) synthesized benchmarks.

systems with a small number of components (C = 2 or 8) for all studied values of  $N \times S$ . When system size grows to 5,000 components or larger, we see significant errors, but only with very large values of  $N \times S$ . For example, for a cluster of 5,000 processors with each processor containing  $N = 10^9$  bits of on-chip storage, the baseline raw error rate would need to scale 2,000 times or more to see a significant error. In practice, terrestrial systems will likely fall into the part of the design space where the SOFR step does not introduce any significant error for SPEC applications.

Focusing on the synthesized workloads (Figure 2.6(b)), for the day workload, we see a significant error using the SOFR step when  $N \times S \ge 10^8$  and  $C \ge 5,000$ . The error increases as these parameters increase. For example, with 12.5MB of storage for each processor ( $N = 10^8$ ) and baseline raw error rate (S = 1), a 5,000 processor cluster sees an error in MTTF of 11%. For a similar cluster of 50,000 processors, the error jumps to 50%. While large, such a cluster is not unrealistic. For the week workload, since the loop size is larger than the day workload, the MTTF errors are correspondingly larger. Thus, the 5,000 and 50,000 processor systems mentioned above respectively see MTTF errors of 32% and 80% for this workload. With larger processors (more storage bits) or larger systems, the error can grow to 90% or more. Thus, for these workloads, the SOFR step incurs significant errors for realistic systems.

Finally, the combined workload (with two SPEC applications) shows a relative error smaller than for the day or week workload, but there is still a significant error for some cases.

In summary, for SPEC benchmarks under current technology and on the ground, the SOFR step gives accurate MTTF estimates. However, in general, for larger scale workloads, care must be taken to examine the workload behavior, number of system components (e.g., processors), and the raw error rate for the components (governed by component size and per-bit or per-element error rate) before applying SOFR.

#### 2.4 Summary

We have examined key assumptions behind the AVF+SOFR method for estimating the architecture level processor MTTF due to soft errors. We use rigorous theoretical analysis backed by simulationbased experiments to systematically explore the applicability of the AVF and SOFR steps across a wide design space. Our analysis and experiments show that while both steps are valid under the terrestrial raw soft error rate values of today's technology for standard workloads (e.g., SPEC), there are cases in the design space where the assumptions of the AVF and SOFR steps do not hold. In particular, for long running workloads with large component-level utilization variations over large time scales, the assumptions are violated for systems with a large number of components and/or with high component-level raw error rate (i.e., large component size and/or large per-bit or per-element raw error rate). Under these conditions, the projected MTTF of the modeled system or chip could show large errors. In general, our work builds a better understanding of the conditions under which the standard AVF+SOFR method may be used to project MTTF accurately, and alerts users to the risks of using the model blindly in conditions where the foundational axioms of the model break down.

## Chapter 3 SoftArch model

As we have shown in Section 2.3.2, the AVF+SOFR method is based on significant assumptions. The assumptions become questionable for some systems in the design space. In this section, we propose a model called SoftArch which can provide fast and accurate analysis of soft errors at the architecture level. We will show in Section 3.4.1 that SoftArch does not need to make the same assumptions as the AVF+SOFR method. In Section 3.4.2, We apply SoftArch to evaluate the MTTF of a processor. In Section 3.4.3, we examine the effect of technology scaling on the architecture level soft error rate taking the architecture level masking effect into consideration.

#### 3.1 Introduction

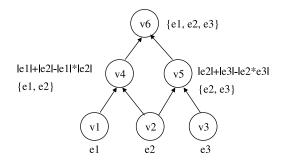

SoftArch works with a high-level architecture timing simulator to track the raw probability of error in the value of each bit (instruction or data) communicated or computed by any pipeline stage in the processor. A value may be erroneous either because (i) it is physically struck by a particle during its residence time in a structure, or (ii) it is the result of a communication of an erroneous value, or (iii) it is computed using one or more erroneous input values. We refer to the first case as error *generation* and to the second and third cases as error *propagation*. To model the error generation probability, we use a combination of residence time and raw SER numbers for storage structures, and a simple abstraction for logic. For error propagation probability, we apply simple probability theory on the error probabilities of the sources of the propagation.

During program execution, SoftArch identifies the values that could affect program outcome. For each such value, it uses the tracked errors for the value and the simulator timing data to determine the probability of failure and time to failure due to that value. This enables determining the mean time to failure using basic probability theory. SoftArch also keeps enough information on the microarchitectural structures occupied by each value to determine the contribution of different structures to the overall MTTF.

SoftArch is based on the first principle of the MTTF calculation, thus it does not need to make the AVF+SOFR assumptions. We perform the same set of experiments for the same designed space as described in Section 2.3. We find that for every point in the design space, the error in the MTTF computed by SoftArch is less than 1% for a single component and 2% for the full system. Thus, SoftArch does not exhibit the discrepancies shown by AVF+SOFR.

Next, we use SoftArch to quantify the MTTF of a modern out-of-order processor and the contribution of different structures to the failure rate, for various SPEC benchmarks. Our results (consistent with, but more comprehensive than, previous studies) are as follows: (1) there is significant architecture level masking of soft errors, (2) there is substantial inter- and intra-application variation in MTTF or failure rate, and (3) there is substantial application-dependent variation in the contribution to the failure rate from different structures. These results motivate selective protection of only the most vulnerable structures and dynamic, application-aware protection schemes.

Finally, as another application, we apply SoftArch to quantify the impact of technology scaling on the architecture level processor soft error rate, taking the architecture level masking effects and workload characteristics into consideration. We scale the same design with the same number of transistors over four technology generations. We find that with scaling, the derating factors for logic structures often decrease, the derating factors for storage elements remain roughly unchanged, and the FIT for the full processor roughly follows the trend for the raw SER of storage structures.

#### **3.2** SoftArch details: a model for architecture level MTTF

The SoftArch model consists of the following components, covered in Sections 3.2.1-3.2.4 respectively. (1) A probabilistic model for *soft error generation* in values residing in storage structures or passing through logic. (2) A model for *soft error propagation*, which results in the propagation of generated errors to other values. (3) A definition of when an erroneous value contributes to *processor failure*. (4) A model for calculating *mean time to failure (MTTF)* for a processor for a given workload.

#### 3.2.1 Error generation model

#### Error generation in storage elements

Current processors include several storage structures such as caches, register files, queues, TLBs, and latches. A soft error in a storage structure occurs when a high energy particle strikes a device in the structure, and the resulting charge collected exceeds the critical charge  $(Q_{crit})$  required to flip the stored bit value. We call this a *raw* soft error.

We seek to determine the probability that a value  $v_i$  residing in a (possibly multiple bit) storage location for time T incurs a raw soft error during T. We assume that if an error occurs, the value is corrupted; i.e., we ignore the low probability that multiple errors could correct the value. It is widely accepted that raw soft errors for storage follow a constant failure rate or exponential time-to-failure distribution model. Let  $\lambda$  denote the raw failure rate, also referred to as the raw soft error rate or SER, for the storage location considered. Then the probability that the value  $v_i$ will incur a raw soft error in time T, denoted  $e_i$ , is  $1 - e^{-\lambda \cdot T}$ . In practice, both  $\lambda$  and T are small enough that we can approximate  $e^{-\lambda \cdot T}$  as  $1 - \lambda \cdot T$ . This gives  $e_i = \lambda \cdot T$ .

Thus, the probability that an error is generated for a value  $v_i$  in a storage location depends on the raw SER for that location,  $\lambda$ , and the residence time of the value in the location, T.  $\lambda$ is determined by circuit layout, technology, and environmental parameters (e.g., the amount of charge stored, charge collection efficiency, and particle flux). There has been extensive work on determining the value of  $\lambda$  using circuit level simulation or measurement (Section 3.3.2). Residence time T depends on the program and the processor architecture, and can be determined through architecture level timing simulation (Section 3.3.1).

#### Error generation in logic elements

Combinational logic elements are used for computation and control within a pipeline stage. A high energy particle strike on a device in a logic circuit may create a current pulse that may affect the value produced by the circuit. This transient effect becomes visible only if it is captured by the subsequent latch. Instead, the transient effect could be masked due to electrical masking (the current pulse attenuates as it goes through the gates in the circuit), logical masking (the current pulse affects parts of the circuit that do not affect the output value), or latch window masking (the corrupted result is not latched because it does not arrive within the required timing window for the latch). Logic SER has been ignored in most prior architectural studies because the above masking makes the effective SER much smaller than that of storage structures. However, as technology scales, these masking effects are diminishing and the logic SER is projected to increase significantly [14].

For our architecture level model, it is desirable to include the above circuit-level masking effects within the *raw logic SER* value. Because these masking effects depend on the circuit layout and inputs, the desired raw logic SER will differ for different logic circuits and even for different inputs. In general, it is hard to abstract all of these effects. We therefore use a simple abstraction consisting of one parameter called  $e_{logic}$  corresponding to each type of logic circuit (e.g.,  $e_{alu}$  for the ALU or  $e_{fpu}$  for the FPU).  $e_{logic}$  is defined to be the probability that, given correct inputs, the result produced by the corresponding circuit at the end of the computation is incorrect because of soft errors.  $e_{logic}$  can be estimated using circuit level SER analysis tools, based on the layout of that logic circuit and technology parameters. In our implementation, we use a simple estimation based on prior work [14] and the gate and latch counts for the logic circuit (Section 3.3.3).

#### 3.2.2 Error propagation model

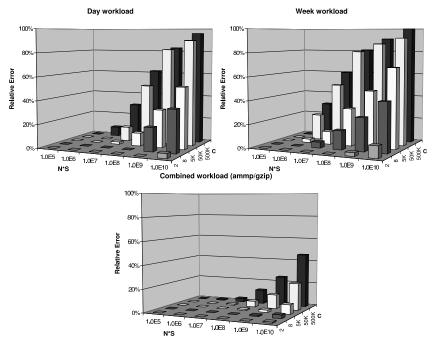

In a processor, values are read from storage locations, possibly processed, and the original or newly computed values are stored elsewhere. (We consider the values stored in the new locations to be new values, even if they are identical to the original ones.) During this process, errors in the original values will propagate to the new values. For example, if the value, v1, in register r1 is corrupted and later used to generate a result r3 = r1 + r2, the error in v1 will propagate to the new value stored in r3.

Conceptually, we would like to track how errors are propagated to new values and determine the probability that a new value is erroneous. These probabilities will then allow us to determine the probability of failure and the mean time to failure (depending respectively on which erroneous values cause failure and when). The probability of error in a newly generated value (say  $v_3$ ) depends on the probability of error in the input values (say  $v_1$  and  $v_2$ ) used to generate  $v_3$ . In general, denoting  $V_i$  to mean the event that value  $v_i$  has an error, denoting  $P(V_i)$  as the probability

Figure 3.1 An example for error propagation.

of  $V_i$ , and assuming that any error in either  $v_1$  or  $v_2$  will cause an error in  $v_3$ , the probability of error in  $v_3$  can be given by  $P(V_3) = P(V_1 \cup V_2) = P(V_1) + P(V_2) - P(V_1 \cdot V_2)$ , where  $V_1 \cdot V_2$  is the event that  $v_1$  and  $v_2$  both have errors.

If the errors in  $v_1$  and  $v_2$  are independent, then  $P(V_1 \cdot V_2)$  is simply  $P(V_1)P(V_2)$ . On the other hand, if the errors are perfectly correlated (e.g., if  $v_2$  was just generated by copying  $v_1$  to another location), then  $P(V_1 \cdot V_2) = P(V_1) = P(V_2)$ . In general, however, the errors in two values could be partially correlated and estimating  $P(V_1 \cdot V_2)$  is more difficult. Accounting for the correlation and determining the resultant probability requires keeping track of the raw errors that were originally responsible for the errors in  $v_1$  and  $v_2$ .