© 2018 Johnathan Alsop

#### SPECIALIZATION WITHOUT COMPLEXITY IN HETEROGENEOUS MEMORY SYSTEMS

BY

JOHNATHAN ALSOP

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2018

Urbana, Illinois

Doctoral Committee:

Professor Sarita V. Adve, Chair & Director of Research Professor Deming Chen Associate Professor Rakesh Kumar Professor Marc Snir Dr. Bradford Beckmann, AMD Research Professor David Wood, University of Wisconsin - Madison

## Abstract

The end of Dennard scaling and Moore's law has motivated a rise in the use of parallelism and hardware specialization in computer system design. Across all compute domains, applications have increasingly relied on specialized devices such as GPUs, DSPs, FPGAs, etc., to execute tasks faster and more efficiently, but interfacing these diverse devices within a heterogeneous system remains an important challenge. Early heterogeneous systems were loosely coupled and lacked a shared coherent memory interface, so specialization was reserved for highly regular code patterns with coarse-grained synchronization requirements. More recently, the need to accelerate applications with more irregular and fine-grained sharing patterns has led to significant research into closer integration of specialized devices.

A single global address space enables improved programmability, communication efficiency, data reuse, and load balancing for emerging heterogeneous applications. Consequently, there have been many attempts to integrate specialized devices and their caches into a single coherent memory hierarchy to improve performance in future systems-on-chip (SoCs). However, coherence is particularly difficult to implement in heterogeneous systems. Differences in parallelism, locality, and synchronization in high-throughput accelerators such as GPUs means that coherence and consistency strategies designed for CPUs are ineffective, and evaluating the performance of alternative strategies is difficult. Recent efforts to implement coherence for such devices involve a simple software-driven coherence strategy combined with complex extensions to a conventional memory consistency model, which guarantees sequential consistency (SC) for programs that are data race-free (DRF). The first extension, scoped synchronization, avoids coherence costs when synchronization is guaranteed to be local, but it requires the use of the heterogeneous race-free (HRF) consistency model, which limits sharing patterns and increases the burden on the programmer. The second extension, relaxed atomics, allows the programmer to avoid costly ordering constraints when they are unnecessary for functionality, but existing consistency models offer complex and often poorly specified semantics when relaxed atomics are used. Once an appropriate coherence and consistency strategy is determined for a device, interfacing it with devices using different strategies poses another critical challenge. Existing integration strategies are incremental, either sacrificing system flexibility or incurring significant added complexity to achieve this goal. A rethinking of heterogeneous coherence and protocol integration from the ground up is needed.

This work lays out a path to implementing flexible and efficient heterogeneous coherence without adding complexity to the consistency model or the system design. To help understand the memory demands of emerging specialized hardware, we first describe a performance analysis tool we developed for highly parallel workloads. Insights from this tool helped guide the development of a collection of coherence and consistency innovations for high-throughput accelerators. On the coherence side, we describe two innovations, DeNovo for GPUs and heterogeneous lazy release consistency (hLRC), which demonstrate that scoped synchronization is not necessary for cache efficiency in high-throughput devices. On the consistency side, this work describes the DRFrlx consistency model, which formalizes safe use cases of atomic relaxation. Again, we offer these benefits while retaining a simple SC-centric DRF consistency model. Finally, to address the challenge of integrating diverse coherence strategies, we present the Spandex coherence interface. Spandex can flexibly and simply integrate devices with a broad range of memory demands in an SoC, and we show how this flexibility enables new performance optimizations that can take advantage of hints about the expected memory demands of an application. Together, these innovations establish a framework for integrating future SoCs that can dynamically adapt to serve the diverse memory demands of future accelerators without incurring complexity for hardware or software designers.

To Rory.

## Acknowledgments

I am fortunate to count many people who have supported me in my academic career. First I'd like to thank all those who served on my thesis committee - Sarita Adve, Brad Beckmann, Deming Chen, Nam Sung Kim, Rakesh Kumar, Marc Snir, and David Wood - who provided valuable feedback and guidance to the development and refinement of this work. Special thanks to Rakesh Kumar, who graciously joined close to the last minute, helping me to avert a minor crisis.

Thank you to all my coauthors on this work: Matt Sinclair, Rakesh Komuravelli, Marc Orr, Brad Beckmann, David Wood, and Sarita Adve. These projects were a collaborative effort, and the research would not have been possible, much less as successful or enjoyable as it was, without each of their contributions. I would gladly collaborate with any of these authors again in the future.

I'd like to thank my advisor, Professor Sarita Adve, for her dedicated guidance, motivation, and support. I am extremely lucky and honored to have had her as an advisor and role model. Her ability to think long term with a focus on the big picture has been critical to the conception, refinement, and completion of most of the innovations in this document. Her persistence and commitment to the students and good ideas that come out of her group have kept our projects moving forward through the low points, and (along with her presentation abilities) have brought attention to our successes. I hope some of this skill and passion has rubbed off on me over the years, and I look forward to working with her in the future.

I'd like to thank the other students and undergraduate researchers in my group - Matt Sinclair, Rakesh Komuravelli, Hyojin Sung, Radha Venkatagiri, Abdulrahman Mahmoud, Muhammad Huzaifa, Gio Salvador, Adel Ejjeh, Khalique Ahmed, Lin Cheng, and Weon Taek Na - for their help and friendship over the years. I especially want to thank Matt Sinclair for his mentorship. As the lead author on much of the work in this document, Matt was a major force in shaping many of these projects and guiding them to completion, and I am very lucky to have worked with him for so long on so many successful projects. I couldn't have asked for a more selfless and capable mentor in my graduate career. Special thanks also to Hyojin Sung and Rakesh Komuravelli for their support in my first years at a time when I required frequent help navigating a new research environment.

Thank you to Brad Beckmann, another important mentor during and after my time as an intern at AMD Research. Without his guidance, commitment, and insights the hLRC work could not have happened. Additionally, his example in navigating the world of academia from a position in industry helped solidify my interest in industry research. I'm excited to be working again with him in my first job out of graduate school.

I'd like to thank all of my teachers and professors who have instructed and inspired me throughout my life, especially Mikko Lipasti at the University of Wisconsin. Mikko inspired my initial interest in computer systems as my professor in ECE 151, and in subsequent interactions he helped fuel that passion, as well as an interest in graduate study.

This work was supported in part by the National Science Foundation under grants CCF-1018796 and CCF-1302641, and by the Center for Future Architectures Research (C-FAR) and the Applications Driving Architectures (ADA) center, Semiconductor Research Corporation program sponsored by MARCO and DARPA. I have also received generous support from the Dan Vivoli Endowed Fellowship and the Rambus Computer Engineering Fellowship.

Thank you to my friends - including but not limited to Jamen, Jeremy, Geoff, Anne, Munoz, Graham, BK, Zia, Dan, Ellen, Sarah, Ta-Hsuan, Ivan, David, Katie, Burt, Heather, Anna, Gio, Kenny, and all the Quality regulars - for helping me stay balanced and being an incredible source of joy and fun times.

Thanks to my dogs, Maeby and Shirley, for mostly being good girls.

Thanks to my family for their constant love and encouragement, and for supporting me in everything I do. My parents, Bob and Karen, have been there for me since day one doing everything everything in their power to ensure my happiness and success. My brother, Jim, has been a good friend starting not long after that. My grandparents, Mary, Chuck, Jean, and Don, have also been significant role models and sources of wisdom, support, and encouragement in my life. My cousins, aunts, uncles, in-laws, and nephew are some of the funniest and kindest people I know, and I've always looked forward to opportunities to spend time with them. Overall I count myself genuinely lucky to be related to such good and loving people whose company I so thoroughly enjoy, and whose support I know I can count on whenever I need it.

Finally, thank you to my wife Rory for loving me, supporting me, and generally being my favorite person. She has contributed to my passion for learning and research through her dedication, her encouragement, and her own considerable achievements. At the same time she inspires an appreciation for life's other pleasures, whether that means relaxing at home with a movie or seeking out fun events and experiences down the street or across the world. My life would be infinitely less exciting and enjoyable without her in it, and I would be much less self-aware.

## **Table of Contents**

| List of | Table          | 2 <b>5</b>                                                               | xi         |

|---------|----------------|--------------------------------------------------------------------------|------------|

| List of | Figur          | 'esx                                                                     | cii        |

| Chapte  | er 1           | Introduction                                                             | 1          |

| 1.1     | Motiv          | ration                                                                   | 1          |

| 1.2     | Contr          | ibutions                                                                 | 5          |

|         | 1.2.1          | GPU Stall Inspector: Performance Characterization in High-Throughput Ac- |            |

|         |                | celerators                                                               | 5          |

|         | 1.2.2          | Efficient GPU Coherence without Scopes                                   | 6          |

|         | 1.2.3          | DRF-Relaxed: Atomic Relaxation with SC-Centric Semantics                 | 6          |

|         | 1.2.4          | Spandex: Efficiently Integrating Heterogeneous Coherence Strategies      | 7          |

|         | 1.2.5          | Dynamic Coherence Specialization                                         | 7          |

| 1.3     | Thesi          | s Organization                                                           | 7          |

| Chapte  | er 2           | GPU Stall Inspector: Performance Characterization in High-Throughput     | t          |

| Acc     |                |                                                                          | 9          |

| 2.1     | Stall          | Classification in GSI                                                    | 10         |

|         | 2.1.1          | Classifying Causes of Instruction Stalls                                 | 10         |

|         | 2.1.2          |                                                                          | 11         |

|         | 2.1.3          |                                                                          | 12         |

|         | 2.1.4          |                                                                          | 12         |

| 2.2     | Case           |                                                                          | 13         |

|         | 2.2.1          |                                                                          | 14         |

|         | 2.2.2          |                                                                          | 16         |

|         | 2.2.3          |                                                                          | 17         |

|         | 2.2.4          |                                                                          | 19         |

| 2.3     |                |                                                                          | 20         |

| Chapte  | ar 3           | Efficient GPU Coherence Without Scopes                                   | 22         |

| 3.1     |                |                                                                          | 22         |

| 0.1     | 3.1.1          |                                                                          | 23         |

|         | 3.1.2          |                                                                          | 23         |

|         | 3.1.3          |                                                                          | $25 \\ 25$ |

| 3.2     |                |                                                                          | $25 \\ 25$ |

| 0.2     | 3.2.1          |                                                                          | $25 \\ 25$ |

|         | 3.2.1<br>3.2.2 |                                                                          | 23<br>26   |

|         | 3.2.2<br>3.2.3 | • 0                                                                      | 20<br>27   |

|         | J.Z.J          | Evaluation                                                               | 41         |

| 3.3    | Heterogeneous Lazy Release Consistency (hLRC+DRF)           | 33        |

|--------|-------------------------------------------------------------|-----------|

|        | 3.3.1 Design                                                | 34        |

|        | 3.3.2 Evaluation                                            | 36        |

| 3.4    | Summary                                                     | 42        |

| Chapte | er 4 DRF-Relaxed: Relaxed Atomics with SC-Centric Semantics | <b>45</b> |

| 4.1    | Background: Relaxed Atomics                                 | 45        |

| 4.2    | Relaxed Atomics Use Cases                                   | 46        |

|        | 4.2.1 Unpaired Atomics                                      | 47        |

|        | 4.2.2 Non-Ordering Atomics                                  | 49        |

|        | 4.2.3 Speculative Atomics                                   | 50        |

|        | 4.2.4 Quantum Atomics                                       | 51        |

| 4.3    | DRF-Relaxed Formal Definitions                              | 52        |

|        | 4.3.1 Definitions for an SC Execution with SC total order T | 53        |

|        | 4.3.2 DRF-Relaxed Model Definition                          | 55        |

| 4.4    | Formalization in Herd                                       | 56        |

|        | 4.4.1 Relaxed Atomics Herd Formalization                    | 56        |

| 4.5    | Evaluation                                                  | 58        |

| 4.6    | Summary                                                     | 60        |

|        |                                                             |           |

| Chapte |                                                             | 64        |

| 5.1    | Background                                                  | 64        |

|        | 5.1.1 Protocol Classification                               | 65<br>68  |

| 5.2    | 5.1.2 Heterogeneous Coherence Solutions                     | 68<br>60  |

| 0.2    | Design                                                      | 69<br>70  |

|        | 1                                                           | 70<br>73  |

|        | 5.2.2 Last Level Cache (LLC)                                | 73<br>78  |

|        | 5.2.3 External Request Interface                            |           |

|        | 5.2.4Translation Unit Responsibilities                      | 80<br>82  |

|        |                                                             | 83        |

| 5.3    | 5.2.6 Overheads                                             | 84        |

| 0.0    | 5.3.1 Cache Configurations                                  |           |

|        | 5.3.1         Cathe Configurations                          |           |

| 5.4    | Evaluation                                                  | 88        |

| 0.4    | 5.4.1 Synthetic Microbenchmarks                             | 89        |

|        | 5.4.2 Collaborative Applications                            | 90        |

| 5.5    | Summary                                                     | 90<br>92  |

| 0.0    | Summary                                                     | 32        |

| Chapte |                                                             | 96        |

| 6.1    | Specialized Coherence Overview                              | 96        |

| 6.2    | Complexity Analysis                                         | 99        |

| 6.3    | Evaluation                                                  |           |

|        |                                                             | 101       |

|        | 6.3.2 Results                                               |           |

| 6.4    | Summary                                                     | 107       |

| Chapte | er 7 Related Work                                           |

|--------|-------------------------------------------------------------|

| 7.1    | Performance Evaluation for High-Throughput Accelerators     |

| 7.2    | Efficient Heterogeneous Coherence and Coherence Integration |

| 7.3    | Atomic Relaxation in Heterogeneous Systems                  |

| 7.4    | Dynamic Coherence Specialization                            |

| 7.5    | Summary                                                     |

|        |                                                             |

| Chapte | er 8 Conclusion and Future Work 114                         |

| 8.1    | Summary of Thesis                                           |

| 8.2    | Future Work and Impact                                      |

|        | 8.2.1 Near-Term Research                                    |

|        | 8.2.2 Long-Term Research                                    |

|        | 8.2.3 Future Impact                                         |

| Refere | nces                                                        |

# List of Tables

| 2.1          | Parameters of the simulated heterogeneous system                                                                                                                       | 16 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $3.1 \\ 3.2$ | Tradeoffs of each GPU coherence and consistency strategy                                                                                                               | 23 |

|              | with local and global scope are denoted with a '_L' and '_G', respectively. $\ldots$ .                                                                                 | 32 |

| 3.3          | Simulated heterogeneous system parameters.                                                                                                                             | 32 |

| 3.4          | Simulated heterogeneous system parameters.                                                                                                                             | 36 |

| 3.5          | Workloads and inputs.                                                                                                                                                  | 36 |

| 5.1          | Coherence strategy classification.                                                                                                                                     | 65 |

| 5.2          | Type and granularity of requests generated for read misses, write misses, and re-                                                                                      |    |

|              | placements of owned data in GPU coherence, DeNovo, and MESI caches. *A De-                                                                                             |    |

|              | Novo ReqV request is issued at word granularity, but the responding device may                                                                                         |    |

|              | include any available up-to-date data in the line.                                                                                                                     | 72 |

| 5.3          | The state transition triggered at the LLC by each request type (Next State) and the request type forwarded to the owning core in the event the data is in O state (Fwd |    |

|              | Msg). An entry of – indicates no transition or forwarded request is necessary.                                                                                         | 75 |

| 5.4          | The state transition and response message triggered at a device by each external                                                                                       |    |

|              | Spandex request. If the target data is not in the expected state when a request                                                                                        |    |

|              | arrives, different behavior may be required (discussed in Section 5.2.3)                                                                                               | 78 |

| 5.5          | Simulated cache configurations.                                                                                                                                        | 85 |

| 5.6          | Simulated heterogeneous system parameters.                                                                                                                             | 86 |

| 5.7          | Collaborative applications communication patterns and execution parameters. CTs                                                                                        |    |

|              | = CPU threads. $TBs = GPU$ thread blocks                                                                                                                               | 88 |

# List of Figures

| 1.1          | Coherence interface in a future heterogeneous system.                                                                                               | 3   |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1          | Stall cycle breakdowns for implicit microbenchmark (normalized to baseline scratch-<br>pad)                                                         | 17  |

| 2.2          | Stall cycle breakdowns for implicit microbenchmark with varying MSHR sizes (nor-<br>malized to baseline scratchpad with 32-entry MSHR).             | 19  |

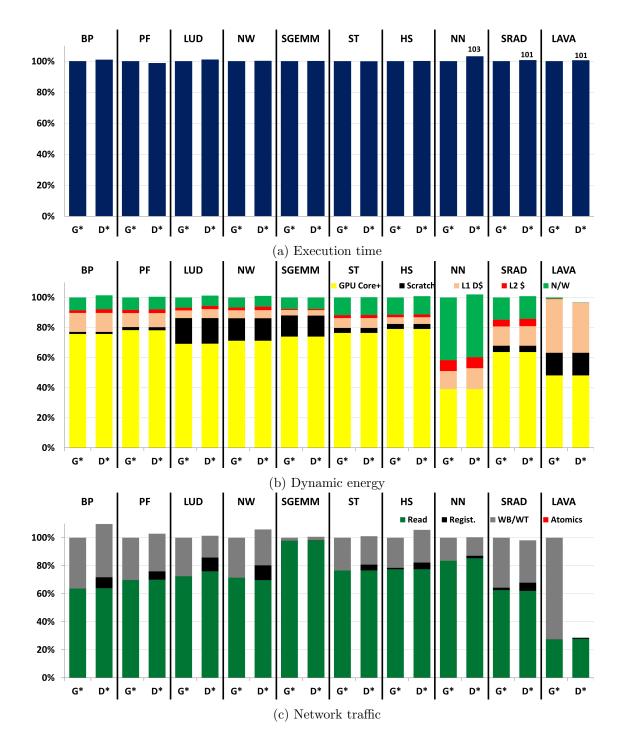

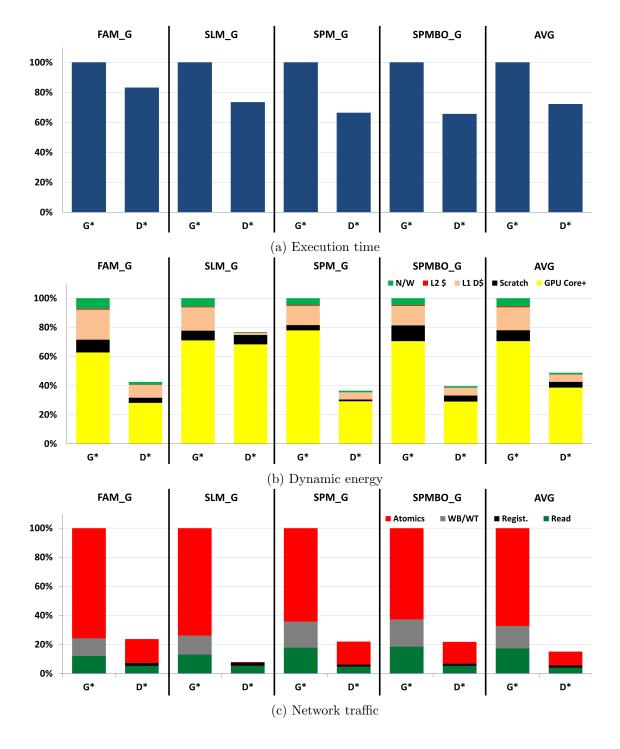

| 3.1          | GPU coherence $(G^*)$ and DeNovo $(D^*)$ configurations with real GPU applications (no intra-kernel synchronization), normalized to $G^*$ .         | 29  |

| 3.2          | GPU coherence $(G^*)$ and DeNovo $(D^*)$ configurations with synchronization benchmarks that use only global synchronization, normalized to $G^*$ . | 30  |

| 3.3          | All configurations with synchronization benchmarks that use mostly local synchro-                                                                   |     |

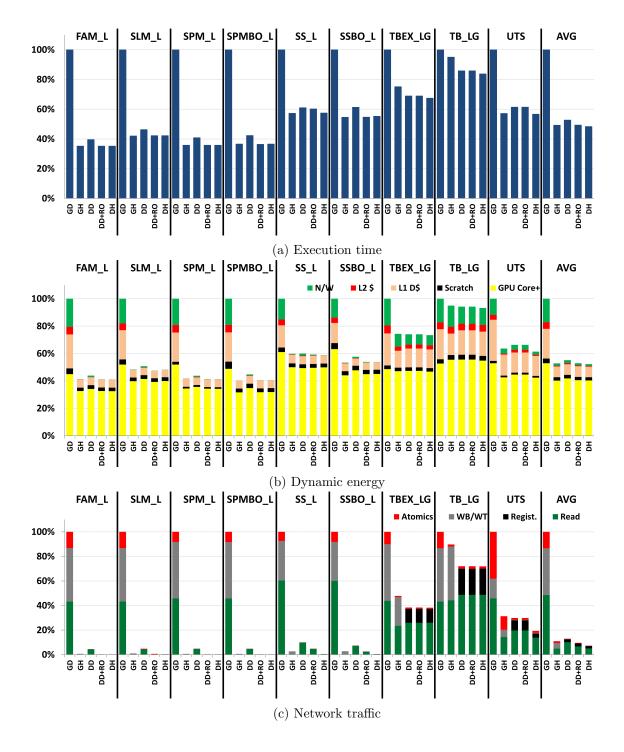

|              | nization, normalized to <i>GD</i> .                                                                                                                 | 31  |

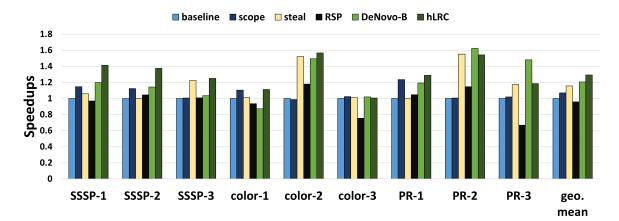

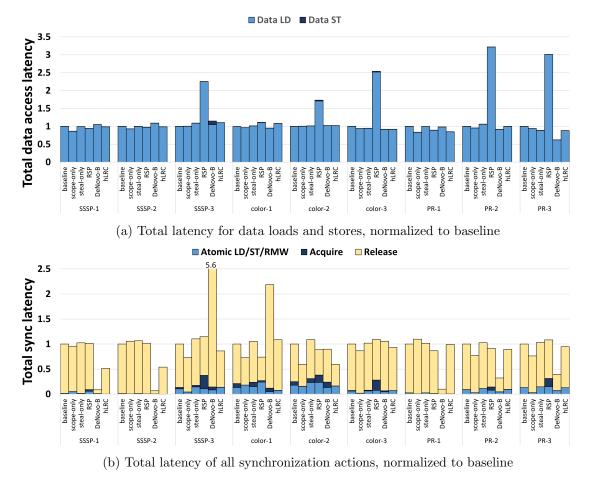

| 3.4          | Performance (speedup relative to baseline).                                                                                                         | 37  |

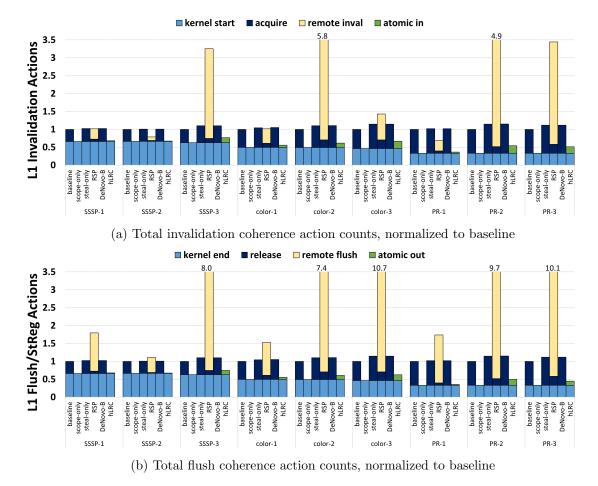

| 3.5          | Breakdowns of invalidation and flush action types.                                                                                                  | 38  |

| 3.6          | Total latency breakdowns for data accesses and synchronization actions                                                                              | 39  |

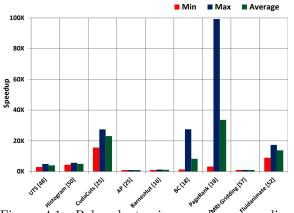

| 4.1          | Relaxed atomics speedup on a discrete GPU.                                                                                                          | 46  |

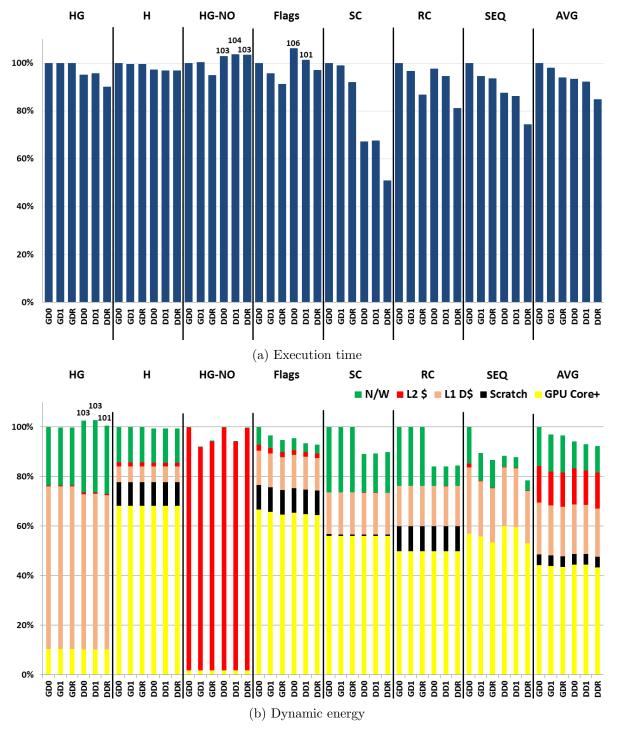

| 4.2          | Execution time and energy for microbenchmarks, normalized to $GD0$                                                                                  | 61  |

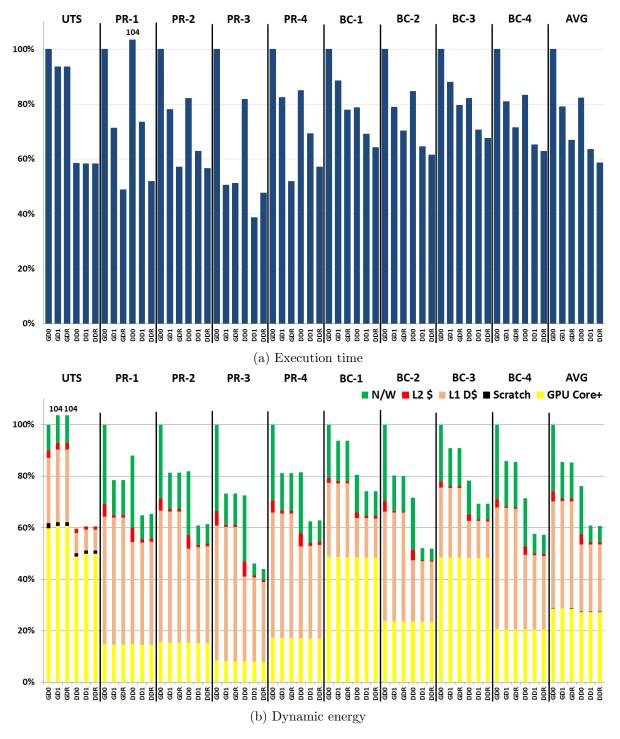

| 4.3          | Execution time and dynamic energy for real applications, normalized to $GD0.$                                                                       | 62  |

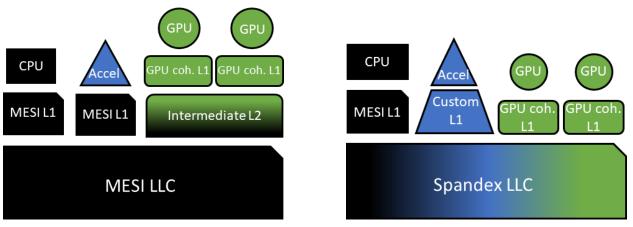

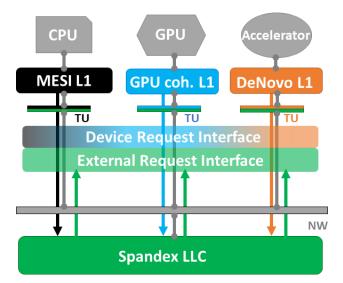

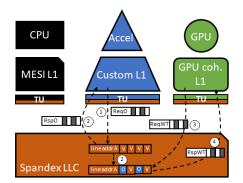

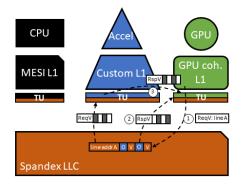

| $5.1 \\ 5.2$ | Comparison of Spandex and a common existing integration strategy                                                                                    | 65  |

|              | eralized network, which may be unordered.                                                                                                           | 70  |

| 5.3          | Handling basic request types at the Spandex LLC.                                                                                                    | 77  |

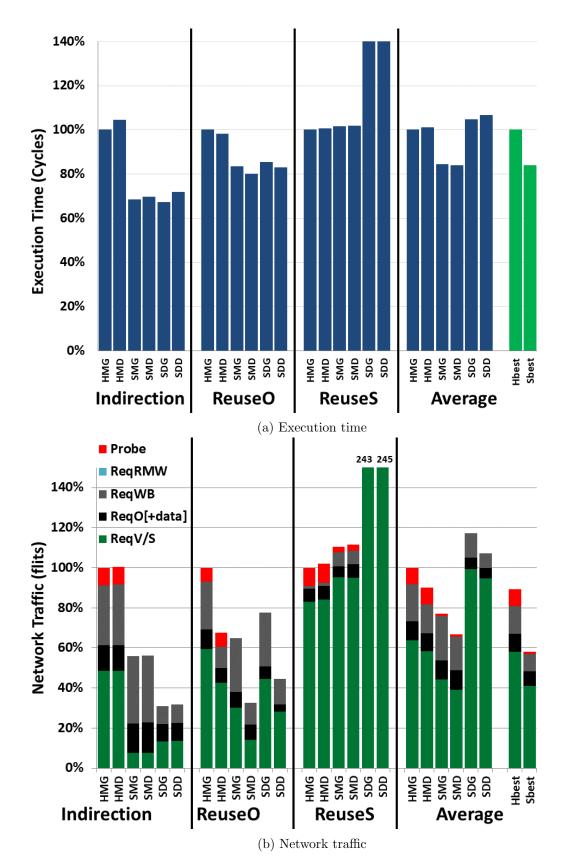

| 5.4          | Synthetic microbenchmarks execution time and network traffic, normalized to HMG.                                                                    | 94  |

| 5.5          | Collaborative applications execution time and network traffic, normalized to HMG                                                                    | 95  |

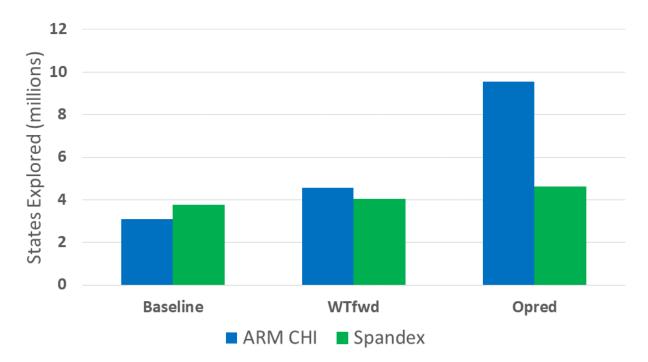

| 6.1          | State space comparison between Spandex and ARM CHI with added optimizations, writethrough forwarding (WTfwd) and owner prediction (Opred)           | 100 |

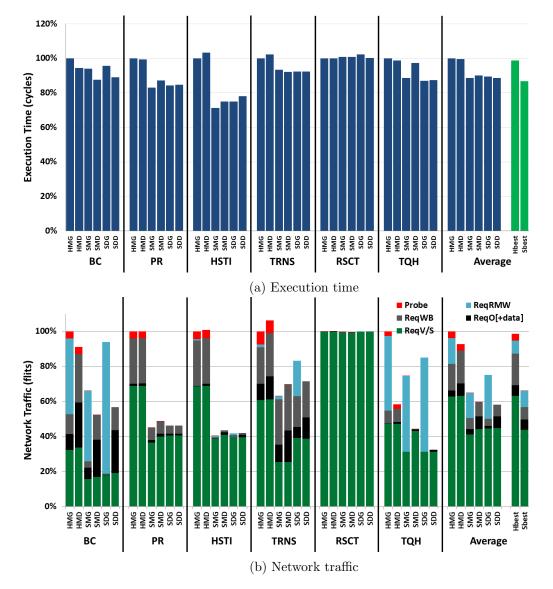

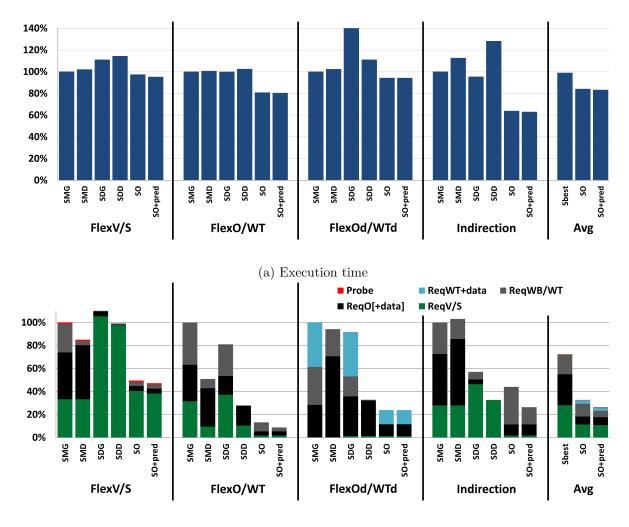

| 6.2          | Synthetic microbenchmarks execution time and network traffic, normalized to SMG.                                                                    | 103 |

# Chapter 1 Introduction

#### 1.1 Motivation

In nearly all compute domains, systems increasingly rely on parallelism and hardware specialization to exceed the limits of single core performance. GPUs, FPGAs, and other specialized devices are being incorporated into everything from mobile devices to supercomputers and data centers, offering new challenges and opportunities to both hardware and software designers. Arguably the most important challenge facing emerging architectures surrounds the efficient movement of data.

In many heterogeneous architectures, the accelerator is loosely-coupled with the host processor and used only to offload coarse-grain tasks with regular data access patterns and infrequent synchronization. A programmer must select a task for acceleration, port it to run on a single accelerator, and explicitly move any data that may be accessed to and from the accelerator's memory space before and after executing the task. This type of architecture avoids the need for costly coherence integration, and for dense regular applications, it can offer well-tuned execution, predictable performance, and efficient hardware utilization.

However, this simple approach lacks generality. Data must be explicitly copied between memory spaces, so workloads with irregular access patterns suffer from wasteful data movement. Synchronization requires conservatively flushing local memories, so applications with fine-grain tasks incur high communication costs. Accelerator memories are not coherent with the rest of the system, so workloads with unpredictable inter-task locality are unable to exploit reuse. This lack of flexibility is a significant and growing problem for two reasons. First, as programmers run out of dense coarse-grain tasks to accelerate, Amdahl's law has motivated a push to deliver efficiency gains for a much broader range of workloads. Applications with irregular sharing patterns, unpredictable control flow, and input-dependent locality (e.g. from the graph analytics, sparse matrix algebra, or sparse machine learning domains) are now targets for acceleration. Irregularity and unpredictability can also lead to load imbalance, which motivates fine-grain synchronization for load balancing mechanisms (and further unpredictability). Second, growth in compute throughput is outpacing growth in memory throughput, creating a memory bottleneck that makes efficient on-chip data movement even more important. Explicit communication through main memory is highly inefficient and suboptimal, especially when that communication is wasteful due to workload irregularity.

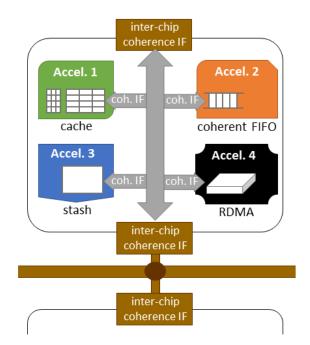

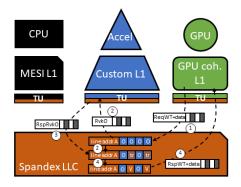

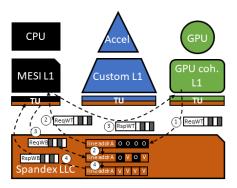

A tightly-coupled accelerator architecture with a unified coherent address space can ease these burdens, enabling greatly improved programmability and communication efficiency for emerging irregular workloads. With a unified coherent memory space, programmers do not need to know in advance where each task will be computed or which data a task will access. Tasks can be dynamically scheduled, load balancing can be performed on-the-fly, data can be communicated only when needed, and devices can exploit implicit reuse in local memory. This explains why many heterogeneous architectures are moving towards tighter host and accelerator integration [30, 31, 86, 108]. At the same time, specialized storage technologies such as scratchpad memory, hardware queues, NVRAM, and high bandwidth 3D stacked DRAM are being incorporated with specialized compute technology in heterogeneous systems to improve performance. Similarly, enabling coherence in these specialized structures is important to offering portability, usability, and flexibility for future workloads. We envision a future where coherent heterogeneous systems can be rapidly prototyped and customized by building upon a simple coherence framework that can flexibly integrate multiple specialized devices with specialized storage across one or more systems-on-chip (SoCs), illustrated in Figure 1.1.

However, there are many challenges to implementing coherence efficiently in any heterogeneous system. In particular, a system designer must optimize two choices in tandem: 1) which coherence and consistency strategy should be used at each individual device or data storage element in the heterogeneous system, and 2) how to efficiently interface the diverse coherence strategies of these heterogeneous devices.

The first challenge, finding the ideal coherence and consistency strategy for a device in a heterogeneous system, will depend heavily on the memory demands of that device. For example, the memory demands of a GPU core differ significantly from those of a CPU core, motivating a dif-

Figure 1.1: Coherence interface in a future heterogeneous system.

ferent coherence solution. CPU applications tend to prefer low latency memory accesses, and as a result they use hardware cache coherence protocols like MESI. Although complex, such protocols are effective at exploiting reuse and reducing latency for many CPU applications. However, unlike CPU applications, traditional streaming GPU applications are throughput-oriented. Thus, the complexity and overheads of MESI are a poor fit for these applications [103]. Instead, today's GPU caches use a software-based coherence protocol that is designed to be simple and lightweight. We refer to this strategy as GPU coherence, and it works by self-invalidating cached data and flushing (writing through) dirty data at synchronization points. This solution avoids the overheads and complexity of MESI-based protocols, and it offers good performance when synchronization is infrequent. However, as GPUs are used to accelerate a broader range of parallel applications that require more frequent synchronization, these invalidation and flush actions can degrade performance significantly [32, 38, 53, 61, 91].

This performance degradation has motivated two significant developments in GPU memory consistency models to allow efficient GPU coherence in the presence of frequent synchronization: scoped synchronization [55] and relaxed atomic semantics [52]. Both of these developments can greatly reduce the overheads of synchronization in GPU caches, but they both also add significant complexity to the commonly used data race-free (DRF) memory consistency model. A DRF memory model offers sequentially consistent (SC) semantics to any program that properly synchronizes between communicating threads. Scoped synchronization additionally requires the programmer to be aware of the relative locations of communicating threads, which may be difficult or impossible depending on the program. Relaxed atomics remove the guarantee of sequential consistency, opening the door to behavior that is difficult to formally specify. The challenges of atomic relaxation have been thoroughly studied for CPUs and are no less relevant in the realm of GPU computing; even when used sparingly by expert programmers, their poorly defined semantics make it difficult to prove that code using relaxed atomics is correct.

The second challenge, how to best interface specialized devices in a coherent heterogeneous system, is difficult because of the widely varying memory demands and coherence strategies used by these devices. Strategies can differ in how they invalidate stale data (writer-invalidate vs. self-invalidate), in how they propagate dirty data (ownership vs. write-through caches), and in the granularity of state and communication (word vs. line). A heterogeneous coherence interface may need to support multiple strategies because no single strategy is able to support the memory demands of the devices being integrated (e.g. CPU and GPU), or simply because the accelerator IP being integrated comes from different vendors that use different protocols. Even within a single device, being able to dynamically optimize the coherence strategy to best fit the executing workload could improve efficiency in future systems. Whether the goal is functionality, composability, or performance, protocol flexibility is important in any heterogeneous coherence interface.

Although there have been many efforts in both academia and industry to efficiently integrate heterogeneous coherence strategies, proposed architectures tend to extend a fixed-granularity MESIbased last level cache (LLC), often using a hierarchical cache structure. Further, most proposed innovations rely on assumptions about sharing patterns in heterogeneous applications. In particular, they assume that sharing is either predominantly hierarchical (i.e., threads can be divided into groups that mostly communicate with each other), at a coarse granularity, or rare and exhibiting minimal locality. As heterogeneous coherent memory becomes more common and as specialized hardware is used to accelerate a more diverse range of applications, these approaches are unable to generalize to a broader range of sharing patterns. A more flexible solution is needed that is able to adapt to efficiently support devices with diverse synchronization frequency, spatial and temporal locality, and throughput and latency requirements.

#### **1.2** Contributions

Motivated by the lack of simple and flexible solutions to the above challenges, the innovations summarized below represent a principled framework for implementing efficient heterogeneous onchip coherence based on simple consistency models that can flexibly and composably integrate the expected diversity of accelerators in future heterogeneous systems. Chapters 2-4 focus on optimizing the coherence and consistency strategy for an individual device, dealing specifically with the unique challenges of conventional caches in high-throughput devices such as GPUs. Chapters 5-6 describe a flexible coherence interface that can be used to integrate diverse coherence protocols on a single chip. In addition, Section 8.2 discusses how the innovations described in this thesis could be applied to benefit a broader range of system architectures and enable future optimizations.

All of the following work has been a collaborative effort. Matthew Sinclair is the lead author on the work described in Section 3.2 and Chapter 4. I am the lead author of the work described in Section 3.3 and Chapters 2, 5, and 6.

### 1.2.1 GPU Stall Inspector: Performance Characterization in High-Throughput Accelerators

As systems increasingly rely on highly parallel accelerators such as GPUs for performance gains, understanding latency bottlenecks in these systems becomes very important to hardware and software development. The first contribution, GPU Stall Inspector (GSI), addresses this need by identifying and classifying stall causes in highly parallel GPU workloads. Unlike prior GPU performance analysis tools, GSI focuses on characterizing the sources of memory stalls. This is of particular importance to designers of heterogeneous systems in which the memory system is the limiting factor for many emerging workloads. With GSI, a system designer can gain insight into the performance bottlenecks of emerging heterogeneous applications and coherence strategies, identifying detailed causes of delays due to synchronization, memory system latency limitations, and memory system throughput limitations. This work originally appeared in ISPASS 2016 [12]. The insights gained from GSI played an important role in developing the following research.

#### 1.2.2 Efficient GPU Coherence without Scopes

While scoped synchronization has emerged as a popular mechanism for efficient heterogeneous coherence, particularly for GPUs, it complicates the DRF memory model and places an undesirable burden on the programmer while also limiting efficient communication patterns.

Chapter 3 describes two techniques to enable efficient coherence for high-throughput devices without complicating the memory model with scoped synchronization. The first technique proposes and evaluates the use of the DeNovo coherence protocol [42], originally proposed for multicore CPUs, to significantly improve data reuse for high-throughput accelerators such as GPUs. The DeNovo protocol obtains ownership for written data rather than writing it through at synchronization points. Since owned data does not need to be invalidated at synchronization points, locality can be exploited in this data even while preserving a relatively simple (scope-free) DRF memory model. This work originally appeared in MICRO 2015 [100] and received an honorable mention in IEEE Micro Top Picks 2016.

The next technique to improve heterogeneous coherence also aims to achieve the benefits of scoped synchronization without adding complexity to the DRF memory model or requiring the GPU cache to support ownership for data writes. Heterogeneous Lazy Release Consistency (hLRC) combines ideas from the DeNovo protocol, remote scope promotion [91], and lazy release consistency for distributed CPUs [60] to automatically detect when a thread is synchronizing locally, and to incur targeted cache invalidation and flush actions only when synchronization may be remote. hLRC represents another way to offer simple and efficient coherence in high-throughput accelerators such as GPUs. While DeNovo exploits locality in stores and atomic accesses to reduce the cost of synchronization in self-invalidating caches, hLRC avoids flush and invalidate actions entirely by exploiting synchronization locality. This work originally appeared in MICRO 2016 [10].

#### 1.2.3 DRF-Relaxed: Atomic Relaxation with SC-Centric Semantics

Relaxed atomics are another popular way to reduce the high costs of synchronization in highthroughput accelerators, even though existing memory models do not provide clear semantics of program behavior when they are used. This work describes the DRF-Relaxed (or DRFrlx) memory model, which reconciles this problem by classifying common use cases of relaxed atomics and defining the conditions for SC-centric execution when using each relaxation type [101]. In this way, DRFrlx enables the benefits of relaxed atomic performance for high-throughput accelerators while preserving SC-centric semantics. This work originally appeared in ISCA 2017 [101].

#### 1.2.4 Spandex: Efficiently Integrating Heterogeneous Coherence Strategies

With Spandex we address the challenge of integrating the diverse coherence strategies that exist in heterogeneous systems. Spandex identifies key orthogonal dimensions in accelerator coherence design, defines a flexible request interface that can flexibly express these dimensions, and presents an integration protocol that efficiently and composably supports these requests. Rather than extending a coherence protocol designed for CPU memory demands, Spandex builds upon the hybrid hardware-software DeNovo protocol, which has been shown to offer scalability and efficiency for both CPU and GPU systems. The end result is an interface that is able to adaptively integrate whichever coherence strategies may be appropriate for future accelerators, while avoiding the complexity and scalability limitations of conventional MESI-based integration solutions. This work originally appeared in ISCA 2018 [11].

#### 1.2.5 Dynamic Coherence Specialization

Flexible coherence interfaces like Spandex create new opportunities for improving coherence efficiency based on the dynamic demands of an executing workload. This section describes memory system optimizations that take advantage of locality, dataflow, and granularity hints that may be available from specialized programming languages, compilation tools, or hardware predictors to improve performance without complicating the DRF memory model. In implementing these extensions we build upon the flexibility and simplicity of the Spandex interface, as well as the insights gained from the analysis and optimization of heterogeneous coherence for emerging applications.

#### **1.3** Thesis Organization

This thesis is organized as follows. Chapter 2 describes how GPU Stall Inspector characterizes memory delay for high-throughput accelerators and demonstrates how it can be used to evaluate and motivate architectural changes in heterogeneous memory systems. Chapter 3 presents DeNovo for GPUs and hLRC, two strategies for simple and efficient coherence in GPUs without the need for scoped synchronization, and compares them against traditional scope-based solutions. Chapter 4 formalizes the DRFrlx memory model and demonstrates how it enables the benefits of relaxed atomics without adding significant complexity. Chapter 5 defines the Spandex coherence interface and evaluates it against a more conventional hierarchical MESI-based protocol. Chapter 6 describes and evaluates optimizations to the Spandex interface that exploit hints about workload memory demands to dynamically optimize memory system performance. Chapter 7 highlights related work, and Chapter 8 summarizes the contributions of this work and discusses potential future research directions.

## Chapter 2

# GPU Stall Inspector: Performance Characterization in High-Throughput Accelerators

Although a common shared memory space offers significant advantages to emerging specialized architectures, the most efficient way to implement coherence in tightly coupled heterogeneous systems is still an open research question. Detailed performance characterization tools are therefore needed to help understand the differences between new heterogeneous coherence strategies, and to guide the development of heterogeneous coherence for future systems and workloads.

Performance characterization in high throughput accelerators such as GPUs is particularly difficult due to the high degree of parallelism. GPU cores can execute hundreds of threads concurrently, so attributing program delay to any single hardware or software element is difficult. While coarsegrained performance metrics such as total execution time may be sufficient for traditional GPU applications where latency attribution is fairly uniform across threads, more detailed information is needed to identify memory performance bottlenecks in less regular workloads. There have been previous efforts to provide more detailed performance profiling metrics [17, 15, 90, 72]; however, this prior work primarily targets discrete (loosely coupled) GPUs and focuses on the causes of delay within the GPU core. <sup>1</sup>

To help understand the detailed sources of memory delay in a tightly coupled CPU-GPU system, we introduce GPU Stall Inspector, or GSI. GSI does more than classify stalls based on the high-level cause of the pipeline delay available at the issue stage. It further subclassifies memory stalls based on the root cause of the memory delay. GSI is able to accomplish this because it is built upon an integrated CPU-GPU simulator based on Multifacet GEMS [82] and GPGPU-Sim. GEMS offers a detailed memory system model (Ruby) which is the source of this additional information.

<sup>&</sup>lt;sup>1</sup>A more detailed description of related work is provided in Section 7.1.

#### 2.1 Stall Classification in GSI

Understanding causes of GPU latency is complicated by the massive parallelism present in GPUs. A GPU consists of multiple cores, each of which can simultaneously execute hundreds of threads that process a highly parallel kernel program. Threads in a GPU are grouped into warps, which proceed together in lockstep through the pipeline. Warps are grouped into thread blocks, and warps in the same thread block are guaranteed to be executed on the same core. In each cycle, a GPU may issue one instruction per issue slot from its warps. We define a stall cycle as any cycle in which no warp instructions are issued by a GPU core. Section 2.1.1 describes the various stall types that may prevent a warp instruction from issuing.

In each stall cycle there may be multiple different warp instructions that are stalled for multiple different reasons. In Section 2.1.2 we describe how a single stall type is chosen from among these stall causes and attributed to each stall cycle. Finally, since we are most interested in memory stalls, in Sections 2.1.3 and 2.1.4 we subclassify memory stalls further based on their underlying causes.

#### 2.1.1 Classifying Causes of Instruction Stalls

When an instruction can be issued in a cycle, the cycle is classified as no stall.

An idle stall occurs when there are no active warps available to issue instructions.

A **control stall** occurs when the instruction supplied by the instruction buffer is not the next instruction to be executed in a warp. If control stalls dominate, there is significant divergence in the kernel code.

A synchronization stall occurs when a warp is blocked due to a pending synchronization operation (acquire, release, or thread barrier). GPUs use acquire and release operations to preserve memory consistency and thread barriers to synchronize threads in a thread block.

A memory data stall occurs when an instruction cannot issue because it is dependent on the result of a pending load. Section 2.1.3 provides more details on the different subcategories of memory data stalls.

A memory structural stall occurs when a memory instruction is unable to issue to the load/store unit because it is full. There are multiple sources of memory structural stalls, which we

describe in more detail in Section 2.1.4.

A compute data stall occurs when an instruction cannot issue because it is dependent on the result of a pending compute (non-memory) instruction.

A compute structural stall occurs when a compute instruction cannot issue because the appropriate compute unit is occupied.

#### 2.1.2 Attributing Stalls to Cycles

GSI stall cycle attribution proceeds in two stages. First, a single stall type is assigned to each warp instruction considered in the issue stage. When classifying the stall cause assigned to an individual warp instruction, priority is given to the stall cause that is most strongly preventing execution. Intuitively, the strength of a stall cause is linked to the likelihood that the instruction will remain stalled in the next cycle. This is not always straightforward to define, and should be tailored to the profiling goals. We specify the prioritization used in Algorithm 1.

After each instruction considered in the issue stage has been classified, the issue cycle itself is classified based on the stall causes of the individual warp instructions. The prioritization we use to classify cycle stall causes is defined in Algorithm 2. Generally, the cycle stall classification is set to match the weakest stall cause found. Intuitively, this is the stall cause of the instruction that was closest to issuing. Since this must be the strongest stall cause for that instruction, removing that stall cause will likely improve performance. However, removing the stall cause may not cause a proportional reduction in the stall count for the removed stall type. A single stalled instruction can be blamed for many stall cycles even if all other instructions are unable to issue for unrelated reasons. Thus, removing the original stall cause and allowing this instruction to issue could simply cause other stall types to dominate.

The "weak" cycle stall classification priority described in Algorithm 2 is not an exact inversion of the "strong" instruction stall classification priority. Memory stalls and synchronization stalls are prioritized over compute stalls in both classification algorithms because we are interested in analyzing the effects of changes to the memory system. Algorithm 1 Instruction Stall Classification

| if No active warps to consider then                                       |

|---------------------------------------------------------------------------|

| classify idle stall                                                       |

| else if The next instruction to issue is unavailable then                 |

| classify control stall                                                    |

| else if Warp is blocked for a synchronization then                        |

| classify synchronization stall                                            |

| else if Instruction has a data hazard on a pending load then              |

| classify memory data stall                                                |

| else if Instruction has a structural hazard on load/store unit then       |

| classify memory structural stall                                          |

| else if Instruction has a data hazard on a pending compute operation then |

| classify compute data stall                                               |

| else if Instruction has a structural hazard on a compute unit then        |

| classify compute structural stall                                         |

| else if Instruction is able to issue then                                 |

| classify <b>no stall</b>                                                  |

| end if                                                                    |

#### 2.1.3 Sub-Classifying Memory Data Stalls

Memory data stalls are subclassified based on where the dependency load was serviced. The subcategories are: L1 cache, L1 coalescing, L2 cache, remote L1 cache, and main memory.

L1 cache stalls mean that instructions have been stalled because they are dependent on loads that are satisfied locally. This can happen if data is used immediately after it is loaded or if there is a delay in the load/store unit. L1 coalescing stalls are due to requests that have missed in the L1 cache but were satisfied by a response for another request to the same line. L2 cache stalls are due to dependencies for requests that are satisfied in the L2 and may mean that the L1 cache is not being efficiently utilized or that the data access pattern does not allow for reuse at L1. Remote L1 cache stalls are caused by dependencies for data requests that are satisfied at a remote L1 core. These are only possible in protocols like DeNovo [110] that enable ownership in L1 caches. Main memory stalls indicate dependencies on accesses to main memory and can occur when the data set is too large to fit in the L2 cache or the L2 is not being utilized efficiently.

#### 2.1.4 Sub-Classifying Memory Structural Stalls

Memory structural stalls occur when a ready memory instruction is blocked from issuing to the load/store unit. Possible causes depend on the memory system being studied, but they are often

Algorithm 2 Issue Cycle Stall Classification

| if At least one instruction was able to issue then           |

|--------------------------------------------------------------|

| classify <b>no stall</b>                                     |

| else if At least one memory structural stall was found then  |

| classify memory structural stall                             |

| else if At least one memory data stall was found then        |

| classify memory data stall                                   |

| else if At least one synchronization stall was found then    |

| classify synchronization stall                               |

| else if At least one compute structural stall was found then |

| classify compute structural stall                            |

| else if At least one compute data stall was found then       |

| classify compute data stall                                  |

| else if At least one control stall was found then            |

| classify control stall                                       |

| else if At least one idle stall was found then               |

| classify <b>idle stall</b>                                   |

| end if                                                       |

due to multiple pending memory accesses. For the memory system configurations considered in this work, memory structural stalls can be caused by a miss status handling register (MSHR) running out of entries (full MSHR), a full store buffer, a bank conflict, a pending release, or an active direct memory access (DMA) operation that is blocking subsequent requests (pending DMA).

Memory structural stalls due to a full MSHR may indicate there is bursty load miss traffic or the MSHR is too small. Similarly, stalls due to a full store buffer may mean there is bursty store miss traffic or the store buffer is too small. Bank conflict stalls can occur if data accesses are not evenly strided across cache or local memory banks. In the system studied, release synchronization operations block stores from issuing until all prior stores are flushed, causing pending release stalls. Similarly, a memory instruction will be blocked if it is trying to access the result of a bulk direct memory access operation (DMA) before the operation is complete, resulting in pending DMA stalls.

#### 2.2 Case Study: Stash vs. Scratchpad+DMA

To demonstrate the value of GSI we use it to evaluate two potential improvements to the scratchpad memory structure used in modern GPUs. We compare the performance of these innovations against a baseline scratchpad implementation and analyze the stall breakdowns of these two innovations for a single application. Using this information we are able to determine the precise causes of performance degradation and motivate changes to the hardware configuration.

#### 2.2.1 Background

Scratchpad memory is a directly addressed memory space that is not kept coherent and is private to a thread block. The scratchpad can be used to cheaply satisfy data accesses that would otherwise need to use the cache. Because all threads in a thread block share the space, scratchpad memory is often used for efficient intra-thread block communication as well.

Despite these benefits, scratchpads suffer from multiple inefficiencies. Typical scratchpad use involves loading data into the scratchpad at the start of a kernel, performing computations on the data in the scratchpad, and then copying the scratchpad data to global memory at the end of the kernel. In this scenario, copying data between the global memory and the scratchpad pollutes the cache and registers and increases instruction count and energy. In addition, the lack of coherence requires that any data that could potentially be accessed by other cores must be conservatively transferred to and from the scratchpad. Thus, if a memory region is only accessed sparsely and unpredictably, the entire region must be copied to and from the scratchpad memory, incurring waste. Because of these inefficiencies, only kernels that access a memory region multiple times in a predictable fashion tend to benefit from using scratchpads.

**D2MA** [57] addresses the inefficiencies of scratchpads by offloading the process of loading data into the scratchpad to a separate DMA. The DMA engine explicitly transfers data into the scratchpad in bulk without polluting the L1 cache or registers. At the start of a kernel a mapping from scratchpad to global data is defined. Scratchpad memory accesses to the mapped region are then blocked (on the first use) until the entire DMA transfer is complete. We approximate D2MA by adding a DMA engine to the baseline scratchpad memory. This implementation, which we refer to as scratchpad+DMA, differs from D2MA in that the DMA engine can transfer data to and from scratchpad (D2MA only loads data into the scratchpad) and a load to an incomplete DMA mapping blocks progress at a core granularity rather than a warp granularity.

**Stash** is a hybrid memory structure that addresses the inefficiencies of scratchpad accesses and cache accesses by making scratchpads a part of the coherent global address space [63]. The stash stores a mapping from local to global data (and the reverse) in a stash map structure. When any

address in the stash mapping is first accessed, the stash map is used to generate a global request to the memory system. When the data returns, it bypasses the cache and is directly loaded into the stash. Subsequent accesses to the mapped address will always hit locally and return without translation. The stash map also enables a GPU core to respond to global requests for data that is dirty in the stash. These coherence mechanisms allow stash data to be loaded on-demand and to be lazily written back, which is not possible with D2MA. This avoids wasteful copies and wasteful instructions involved in managing a scratchpad.

All three configurations use DeNovo coherence [42] for GPU and CPU caches and for the stash (described in detail in Section 3.2). Both scratchpad+DMA and stash improve upon scratchpad memory because the data transfers to and from scratchpad/stash memory bypass the cache. The stash also implicitly transfers data between the local and global address spaces. The main difference between stash and scratchpad+DMA is that stash data is kept coherent with the shared global memory. This means that stash accesses can generate global load requests on-demand and that dirty data can be lazily written back because it is globally visible. In contrast, scratchpad with DMA must conservatively transfer all data into the scratchpad at the start of a kernel, and conservatively write back any potentially modified data at the end of the kernel.

The DMA data movement pattern can be helpful or harmful. Bulk reads and writes happen in parallel and can be a very effective preloading technique for avoiding the memory latency of successive on-demand load misses. However, scratchpad accesses to a pending DMA allocation must stall until the entire DMA transfer completes. This latency combined with the congestion caused by bursty DMA traffic may negatively affect performance.

The tradeoffs of stash memory and scratchpad+DMA result in differences in the memory system that can reduce some sources of performance degradation but increase others. We use GSI to better understand how these differences affect GPU performance, focusing on one microbenchmark: Implicit.

Implicit is a synthetic microbenchmark used by Komuravelli, et al. to evaluate the benefits of stash [63]. In the Implicit microbenchmark, an array of data is allocated and mapped to scratch-pad/stash memory. Each thread block is assigned a chunk of the array. Each thread reads an element in the chunk, performs a computation on the element, and writes the result back to the same location in memory.

| CPU Parameters                      |                     |  |  |

|-------------------------------------|---------------------|--|--|

| Frequency                           | $2~\mathrm{GHz}$    |  |  |

| Cores                               | 1                   |  |  |

| GPU Parameters                      |                     |  |  |

| Frequency                           | $700 \mathrm{~MHz}$ |  |  |

| GPU cores used                      | 1                   |  |  |

| Scratchpad/Stash Size               | 16 KB               |  |  |

| Number of Banks in Stash/Scratchpad | 32                  |  |  |

| Memory Hierarchy Parameters         |                     |  |  |

| L1 and Stash/Scratchpad hit latency | 1 cycle             |  |  |

| Remote L1 and Stash hit latency     | 35-83 cycles        |  |  |

| L1 Size (8 banks, 8-way assoc.)     | 32 KB               |  |  |

| L2 Size (16 banks, NUCA)            | 4 MB                |  |  |

| L2 hit latency                      | 29-61 cycles        |  |  |

| Memory latency                      | 197-261 cycles      |  |  |

Table 2.1: Parameters of the simulated heterogeneous system.

This microbenchmark highlights the advantage of implicitly loading data into scratchpad/stash memory and is representative of applications that access data in a regular streaming manner. Stash implicitly moves data from global to scratchpad/stash memory while scratchpad+DMA uses a DMA engine to reduce the overheads of explicit data movement, so both configurations should improve performance over the baseline scratchpad configuration. By applying GSI to this application and analyzing the stall breakdown, we can understand the impact of each of the above effects on overall performance, and we use this information to motivate a change in the hardware system used.

#### 2.2.2 Methodology

We use GSI to compare D2MA and stash storage strategies for the Implicit microbenchmark. GSI is implemented on top of an integrated CPU-GPU architectural simulator. The Simics [78] full system simulator models the CPU cores, GPGPU-Sim [17] models the GPU cores (the modeled GPU is similar to an NVIDIA GTX 480), the Wisconsin GEMS memory timing simulator [82] models the memory system, and Garnet [7] models the interconnect. The system contains 1 CPU core and 15 GPU cores distributed across a 4x4 mesh network. Each core has a private L1 and all cores share a banked last level L2 cache. The simulated stash memory is identical to that used in the original stash publication [63]. For simplicity, only one GPU core is utilized in the evaluation of the Implicit microbenchmark. Table 2.1 summarizes the key architectural parameters of our simulated

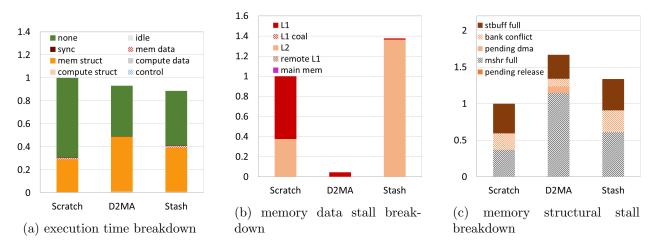

Figure 2.1: Stall cycle breakdowns for implicit microbenchmark (normalized to baseline scratchpad).

system. A similar simulation setup is also used for some subsequent work in this thesis. While past studies have validated individual components of this simulator, the full integrated simulator differs from existing hardware in its flat integrated cache structure, and as a result no full system validation of this integrated simulator has been attempted. The changes required to implement GPU stall profiling are minimal. GSI increases simulation time by on average 5% for a set of representative workloads, with this proportion decreasing as input sizes increase. The introduction of GSI does not affect simulation results, and all results are deterministic.

#### 2.2.3 Evaluation

Figure 2.1a shows the GPU execution time breakdown of the implicit microbenchmark. Figures 2.1b and 2.1c show the memory data stall and memory structural stall subclassifications, respectively. We use these results to identify causes of performance disparity between stash and scratchpad+DMA memory configurations.

Figure 2.1a shows that the number of "no stall" cycles is reduced by 36% and 31% for scratchpad+DMA and stash, respectively. This occurs because both the scratchpad+DMA and stash configurations reduce instruction count. The scratchpad+DMA configuration does this by offloading the loads to its DMA engine, and the stash does this by loading mapped data on-demand from global memory into the stash. Thus, neither configuration needs initial scratchpad load and store instructions that pollute the registers or L1 cache. However, the reduction in "no stall" cycles is not uniform, and is offset by increases in other stall types. This kind of benefit offset is not uncommon when profiling stall causes.

In the case of the Implicit microbenchmark, the "no stall" cycle reductions in scratchpad+DMA and stash are offset primarily by 67% and 34% increases in memory structural stalls, respectively. Scratchpad has fewer memory structural stalls because the explicit transfer of scratchpad data serves to restrict the rate of requests to the memory system. At the start and end of the kernel, the baseline scratchpad implementation issues many concurrent loads and stores (respectively) to the memory system, incurring memory structural stalls due to bank conflicts, a full store buffer and a full MSHR. However, these memory operations are interleaved with instructions that perform address calculations and scratchpad store instructions, so the rate at which global memory loads are issued to the memory system is limited. As a result, the number of memory structural stalls is also limited.

In comparison, scratchpad+DMA does not need to process any data transfer instructions and is able to issue load requests to the memory system as fast as the DMA engine allows (one per cycle). This increased request rate causes the MSHR to fill up faster. These generated requests bypass the pipeline and the cache, so bank conflicts are insignificant, but as soon as a normal memory access tries to issue to the global memory or scratchpad memory, it is blocked due to a full MSHR or a pending DMA (only for dependent instructions).

Stash generates a global memory access at the first load of each stash data word. Since the stash is directly addressed, fewer instructions are needed to compute stash addresses than are needed to compute the target address for requests to global memory in the baseline scratchpad configuration. This means fewer instructions are interleaved with the memory instructions, and memory instructions are issued to the memory system at a faster rate than for baseline scratchpad. This increased memory request rate increases the amount of memory structural stalls due to a full MSHR, a full store buffer, and bank conflicts.

Overall, the stall breakdowns tell us that scratchpad+DMA and stash are able to improve performance, but the amount of time saved is offset by additional stalls caused by increased memory request frequency. Furthermore, although there is a difference in data stalls, it is insignificant.

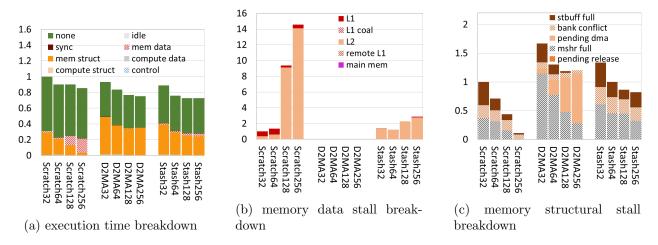

Figure 2.2: Stall cycle breakdowns for implicit microbenchmark with varying MSHR sizes (normalized to baseline scratchpad with 32-entry MSHR).

#### 2.2.4 MSHR Sensitivity

Since MSHR stalls are significant for this microbenchmark, we investigate the effect of increasing MSHR size on performance. We run the Implicit microbenchmark on all three configurations while increasing MSHR size from 32 to 256. We also scale the store buffer size with the MSHR size to prevent store buffer stalls from becoming the new bottleneck. Figure 2.2a shows the results normalized to baseline scratchpad using an MSHR with 32 entries.

The decrease in full MSHR stalls shows that increasing MSHR size benefits all configurations. However, each configuration benefits from the increased MSHR size in different ways. A 256entry MSHR completely eliminates full MSHR stalls for the baseline scratchpad configuration, but memory data stalls significantly increase (13X compared to its original value). Memory data stalls increase for the scratchpad configurations because the instruction following the explicit load (a store of the value to scratchpad memory) is dependent on the result of that load. Although many more explicit loads are able to issue with a larger MSHR, the next instruction will need to block until the load has completed.

As MSHR size increases, MSHR stalls decrease for the scratchpad+DMA configuration. However, memory structural stalls due to pending DMA requests significantly increase as MSHR size increases (8.9X more with a 256-entry MSHR). These memory structural stalls increase because the first scratchpad accesses occur early in the application, which causes threads to be blocked due to a pending DMA soon after the application begins. Increasing MSHR size also reduces MSHR stalls for the stash configuration by allowing a greater number of threads to concurrently issue memory requests (implicitly in the case of the stash configuration). Although MSHR stalls decrease, memory data stalls increase (2.1X compared to the original value) because the issued requests have not completed before a dependent instruction needs to use the returned value. However, the increase is less significant for stash compared with scratchpad. This is because the scratchpad implementation must wait for all loads to the scratchpad to complete before proceeding to the compute phase. The stash configuration, on the other hand, will issue loads on-demand within the compute phase. Although many warps will still be blocked waiting for the result of a load to stash memory, there are more active threads during the compute phase that can utilize the issue slots with useful work. As a result, stash achieves higher core utilization than scratchpad and experiences a smaller increase in memory data stalls as MSHR size increases.

Overall, these results show that increasing MSHR size improves performance for all configurations. However, alleviating this bottleneck causes other stall sources to increase. For the scratchpad configuration, increasing the number of MSHRs does not help as much because of data dependencies. Increasing MSHR size is more beneficial for the scratchpad+DMA configuration, which sidesteps the data dependencies by prefetching data. However, because the scratchpad data is used early in the application, memory structural stalls due to pending DMA requests increase for the scratchpad+DMA configuration. The stash configuration also benefits from increased MSHR size but is better able to utilize the core by only blocking scratchpad loads at the granularity of warps (as discussed in Section 2.2.1). Thus, these results demonstrate the benefits of the stash's hybrid memory organization.

#### 2.3 Summary

GSI delivers a detailed breakdown of every stall cycle in the execution of a GPU application. This information can help to identify performance bottlenecks in emerging heterogeneous applications, confirm and explain unexpected heterogeneous simulation results, help understand performance differences between heterogeneous coherence strategies, and motivate changes to hardware and software to accelerate high-throughput workloads. As new strategies are proposed to enable efficient heterogeneous coherence for emerging workloads with irregular sharing and synchronization, these insights only grow in importance.

Overall, GSI has been a crucial tool in the development of subsequent work in this thesis. Although GSI is focused specifically on stall causes in GPU systems, the concepts of stall cause prioritization and memory stall sub-classification can be applied to other types of highly parallel specialized hardware as well.

### Chapter 3

# Efficient GPU Coherence Without Scopes

Since coherence overheads and scalability limitations make MESI coherence a poor fit for GPU workloads, modern GPUs use a software-based coherence strategy, which we refer to as GPU coherence. Instead of tracking owners and sharers, GPU coherence triggers bulk cache invalidation and flush actions at specified points to keep caches coherent.

GPU coherence is simple to implement, but it can be very inefficient if the bulk flushes and invalidations are frequent. There have been many efforts to limit the impact of these actions, but perhaps the most common are scoped synchronization and relaxed atomics, both of which add significant complexity to the memory model. In the following sections we discuss the limitations of scoped synchronization and related techniques, and we propose two changes to the GPU *coherence protocol* that enable similar efficiency without requiring complex changes to the consistency model: DeNovo for GPUs (Section 3.2) and heterogeneous lazy release consistency (hLRC, Section 3.3). Chapter 4 discusses the challenges of relaxed atomics and proposes an extension to the DRF *consistency model* that offer simple semantics for practical use cases of atomic relaxation.

#### 3.1 Background

In this chapter we describe existing strategies for efficient GPU coherence and consistency and propose simpler and more flexible alternatives. Table 3.1 summarizes the tradeoffs of each GPU coherence and consistency strategy discussed. Each strategy is classified by whether it is simple and scalable, whether it enables dynamic sharing (defined in Section 3.1.3), and what memory access properties it relies on to avoid flush and invalidation overheads and achieve efficient coherence.

| Coherence+       | Simple    | Scalable | Efficient       | Avoids synch. overheads for: |             |

|------------------|-----------|----------|-----------------|------------------------------|-------------|

| Consistency      | semantics | Scalable | dynamic sharing | High synch.                  | Locality in |

|                  |           |          |                 | locality                     | owned data  |

| GPU coh.+DRF     | 1         | 1        | ✓               | ×                            | ×           |

| GPU coh.+HRF     | ×         | ✓        | ×               | $\checkmark$                 | ×           |

| GPU coh.+HRF+RSP | ×         | ×        | ✓               | ✓                            | ×           |

| DeNovo+DRF       | 1         | 1        | ✓               | ×                            | ✓           |

| DeNovo+HRF       | ×         | 1        | ✓               | ✓                            | ✓           |

| hLRC+DRF         | ✓         | 1        | ✓               | ✓                            | ×           |

Table 3.1: Tradeoffs of each GPU coherence and consistency strategy.

#### 3.1.1 Data Race Free Memory Models (GPU coh.+DRF)

Our baseline GPU coherence implementation assumes a relatively simple memory consistency model that guarantees sequentially consistent behavior for data race-free (i.e., properly synchronized) programs, also called DRF. Under the DRF memory model, defined by Adve and Hill [4], data accesses are distinguished from synchronization (or atomic) accesses in software. A program is data race-free if, in every SC execution of the program, any two conflicting data accesses from different threads are ordered by a happens-before relation, which is essentially a chain of paired synchronization accesses (e.g., the release and acquire of a lock protecting a critical section). If no such chain exists between conflicting data accesses from different threads, this constitutes a *data race*. A system is DRF compliant if every execution of a DRF program is guaranteed to be sequentially consistent. As long as bulk cache flush and invalidate actions are performed at every synchronization access (or kernel boundary, or memory fence), GPU coherence is compliant with the DRF memory model and can guarantee SC behavior for any DRF program.

Using DRF with GPU coherence combines simple semantics with a scalable protocol. However, it requires flush and invalidates to be performed at every synchronization action, which can be very inefficient if synchronization is frequent.

#### 3.1.2 Scoped Synchronization (GPU coh.+HRF)

One common strategy to reduce the cost of synchronization in GPU caches is to use scoped synchronization. Scoped synchronization allows the programmer to avoid cache flushes and invalidations when they are known to be unnecessary. This can significantly improve performance, but it also adds a great deal of complexity to the memory consistency model. Despite this complexity, the notion of scoped synchronization is ubiquitous in GPU memory models and is present in both the HSA memory consistency model [51] as well as (less precisely) in the CUDA programming specification [88], two of the most widely used GPU memory models in industry.